#### University of Kentucky

## **UKnowledge**

Theses and Dissertations--Electrical and Computer Engineering

**Electrical and Computer Engineering**

2023

## A Phase Change Memory and DRAM Based Framework For Energy-Efficient and High-Speed In-Memory Stochastic Computing

Supreeth Mysore University of Kentucky, ssh366@uky.edu Digital Object Identifier: https://doi.org/10.13023/etd.2023.191

Right click to open a feedback form in a new tab to let us know how this document benefits you.

#### **Recommended Citation**

Mysore, Supreeth, "A Phase Change Memory and DRAM Based Framework For Energy-Efficient and High-Speed In-Memory Stochastic Computing" (2023). *Theses and Dissertations--Electrical and Computer Engineering*. 192. https://uknowledge.uky.edu/ece\_etds/192

This Doctoral Dissertation is brought to you for free and open access by the Electrical and Computer Engineering at UKnowledge. It has been accepted for inclusion in Theses and Dissertations--Electrical and Computer Engineering by an authorized administrator of UKnowledge. For more information, please contact UKnowledge@lsv.uky.edu.

## STUDENT AGREEMENT:

I represent that my thesis or dissertation and abstract are my original work. Proper attribution has been given to all outside sources. I understand that I am solely responsible for obtaining any needed copyright permissions. I have obtained needed written permission statement(s) from the owner(s) of each third-party copyrighted matter to be included in my work, allowing electronic distribution (if such use is not permitted by the fair use doctrine) which will be submitted to UKnowledge as Additional File.

I hereby grant to The University of Kentucky and its agents the irrevocable, non-exclusive, and royalty-free license to archive and make accessible my work in whole or in part in all forms of media, now or hereafter known. I agree that the document mentioned above may be made available immediately for worldwide access unless an embargo applies.

I retain all other ownership rights to the copyright of my work. I also retain the right to use in future works (such as articles or books) all or part of my work. I understand that I am free to register the copyright to my work.

## **REVIEW, APPROVAL AND ACCEPTANCE**

The document mentioned above has been reviewed and accepted by the student's advisor, on behalf of the advisory committee, and by the Director of Graduate Studies (DGS), on behalf of the program; we verify that this is the final, approved version of the student's thesis including all changes required by the advisory committee. The undersigned agree to abide by the statements above.

Supreeth Mysore, Student Dr. Ishan Thakkar, Major Professor Dr. Daniel Lau, Director of Graduate Studies A Phase Change Memory and DRAM Based Framework For Energy-Efficient and High-Speed In-Memory Stochastic Computing

#### DISSERTATION

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the College of Electrical and Computer Engineering at the University of Kentucky

By Supreeth Mysore Shivanandamurthy Lexington, Kentucky

Director: Dr. Ishan G. Thakkar, Assistant Professor of Electrical and Computer Engineering Co-Director : Dr. Sayed Ahmad Salehi, Assistant Professor of Electrical and Computer Engineering Lexington, Kentucky 2023

Copyright<sup>©</sup> Supreeth Mysore Shivanandamurthy 2023

#### ABSTRACT OF DISSERTATION

#### A Phase Change Memory and DRAM Based Framework For Energy-Efficient and High-Speed In-Memory Stochastic Computing

Convolutional Neural Networks (CNNs) have proven to be highly effective in various fields related to Artificial Intelligence (AI) and Machine Learning (ML). However, the significant computational and memory requirements of CNNs, especially the multiply-accumulate (MAC) operations that are fundamental building blocks of CNNs, make their processing highly challenging. As the input dataset size increases, the traditional processor-centric, von-Neumann computing architectures become ill-suited for processing CNNs because they exponentially increase the latency and energy costs of processing CNNs.

To overcome these challenges, researchers have explored the Processing-In-Memory (PIM) technique, which involves placing the processing unit inside or near the memory unit. This approach reduces data migration length and utilizes the internal memory bandwidth at the memory bank and subarray levels. However, developing an efficient PIM-based system with minimal hardware complexity remains a significant challenge.

The proposed PIM solution in this thesis report suggests utilizing different memory technologies, such as Dynamic RAM (DRAM) and phase change memory (PCM), with stochastic arithmetic and minimal add-on logic. Stochastic computing is a technique that uses pseudo-random numbers to perform arithmetic operations. This technique reduces hardware requirements for CNNs' arithmetic operations, making it possible to implement them with simple logic gates.

This thesis report details techniques and architectures to enable DRAM and PCM-based PIM systems that can employ stochastic arithmetic to accelerate CNNs. The detailed topics include PCM-based scalable Stochastic Number Generator (SNG), DRAM-based stochastic MAC accelerator for CNNs, non-volatile memory (NVM) class PCRAM-based MAC accelerator for CNNs, and DRAM-based stochastic to binary conversion (StoB). The report also identifies future research directions to enable highly scalable, energy-efficient, and high-speed PIM accelerators for CNNs. for the proposed designs, including in-situ PCRAM-based SNG, ODIN (A Bit-Parallel Stochastic Arithmetic Based Accelerator for In-Situ Neural Network Processing in Phase Change RAM), ATRIA (Bit-Parallel Stochastic Arithmetic Based Accelerator for In-DRAM Deep Learning), and presents initial findings for these ideas.

In summary, the proposed solution in the report offers a comprehensive approach to address the challenges of processing CNNs. The proposed designs have the potential to significantly improve the energy and time efficiency of accelerating CNNs. Using Stochastic Computing with different memory technologies enables the development of efficient PIM-based systems with minimal hardware overheads and complexity, providing a promising path for the future of CNN-based applications.

KEYWORDS: In-Memory Computing, Convolution Neural Network, Stochastic Computing, Artificial Intelligence

Author's signature: Supreeth Mysore Shivanandamurthy

Date: May 5, 2023

A Phase Change Memory and DRAM Based Framework For Energy-Efficient and High-Speed In-Memory Stochastic Computing

> By Supreeth Mysore Shivanandamurthy

> > Director of Dissertation: Dr. Ishan G. Thakkar

Co-Director of Dissertation: Dr. Sayed Ahmad Salehi

Director of Graduate Studies: Dr. Daniel Lau

Date: May 5, 2023

DEDICATED TO MY FAMILY AND TEACHERS Thanks for leading me from the darkness of ignorance to the quest for the immortality of knowledge.

#### ACKNOWLEDGMENTS

I would like to take this opportunity to express my gratitude to several individuals who have contributed significantly to the successful completion of my work. Without their support, guidance, and motivation, this accomplishment would not have been possible.

First and foremost, I would like to extend my heartfelt gratitude to my advisor, Dr. Ishan Thakkar, for his unwavering support and guidance throughout my research. Dr. Thakkar has consistently provided me with the latest ideas, relevant literature, and infrastructure, which have been critical to the completion of my work. His constant encouragement and constructive feedback have been invaluable, and I am grateful for his mentorship.

I would also like to acknowledge my family, who has been my pillar of strength throughout this journey. Their unconditional love, support, and sacrifice have been an inspiration to me, particularly during the challenging times of the pandemic. Their unwavering encouragement and motivation have been the driving force behind my accomplishments, and I am grateful for their unwavering support.

Moreover, I would like to express my appreciation to my fellow labmates at UCAT lab, UKY, for their insightful discussions and collaborative efforts. Their support, camaraderie, and shared knowledge have been instrumental in making my research journey an enjoyable and memorable one.

Finally, I would like to thank Dr. Salehi for his support and guidance during my research studies. His valuable insights, suggestions, and expertise have been instrumental in shaping my work, and I am grateful for his mentorship.

Once again, I extend my sincere appreciation to all those who have contributed to the successful completion of my work, and I look forward to continuing my research journey with their support and guidance.

iii

## TABLE OF CONTENTS

| Acknowledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                  | iii                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                  | vi                                                                   |

| List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                   | viii                                                                 |

| Chapter 1  Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1<br>2<br>3                                                          |

| Chapter 2 Background and Related Work                                                                                                                                                                                                                                                                                                                                                                                                                            | 4<br>4<br>4<br>5                                                     |

| Chapter 3Scalable Stochastic Number Generator for Phase Change Memory (PCM)<br>based In-memory Stochastic Processing3.1Chapter Overview3.2Background: Phase change memory3.3Stochastic Number Generator3.4Results3.5Summary                                                                                                                                                                                                                                      | 12<br>12<br>12<br>13<br>14<br>15                                     |

| Chapter 4An Accelerator Based on Parallel SC for In-PCRAM Deep Learning<br>Applications4.1Chapter Overview4.2Introduction4.3Related work and motivation4.4Phase change Ram (PCRAM) architecture4.5Stochastic arithmetic4.6ODIN Framework: overview4.7Integration with heterogeneous computing system4.8Hardware modifications in PCRAM banks4.9Hardware for multiply-accumulate (MAC) operations4.10Hardware for activation and pooling functions4.13Conclusions | 16<br>16<br>17<br>18<br>19<br>19<br>20<br>21<br>23<br>25<br>26<br>28 |

| Chapter 5  A Parallel SC Based In-DRAM CNN Accelerator    5.1  Chapter Overview                                                                                                                                                                                                                                                                                                                                                                                  | 29<br>29                                                             |

| 5.2 Introduction                                                                      | 29  |

|---------------------------------------------------------------------------------------|-----|

| 5.3 Concept of Bit-Parallel Rate-Coded Unary (stochastic) computing                   | 30  |

| 5.4 ATRIA: Overview                                                                   | 32  |

| 5.5 Evaluation                                                                        | 37  |

| 5.6 Conclusions                                                                       | 41  |

| Chapter 6 A Substrate for In-DRAM StoB for CNN Applications                           | 42  |

| $6.1$ Abstract of the chapter $\ldots$                                                | 42  |

| 6.2 Introduction                                                                      | 42  |

| 6.3 Background and related work                                                       | 44  |

| 6.4 Proposed technique to convert the rate coded unary to temporal coded unary        | 45  |

| 6.5 Overview of Our AGNI Substrate                                                    | 46  |

| 6.6 Operation of Our AGNI Substrate                                                   | 47  |

| 6.7 Evaluation                                                                        | 53  |

| 6.8 Conclusion and future scope                                                       | 55  |

|                                                                                       | 50  |

| Chapter 7 Conclusions                                                                 | 56  |

| Chapter 8 Future Direction 1: Optimized GDAC-based SNG, Analysis and Miti-            |     |

| gation of the Impacts of PCRAM Reliability Issues                                     | 57  |

| 8.1 Introduction                                                                      | 57  |

| 8.2 Problems in the existing OPAMP-based SNG                                          | 57  |

| 8.3 Key ideas/Approaches                                                              | 58  |

| 8.4 Goals of this work                                                                | 59  |

| Chapter 9 Future direction 2: PSCA – Stochastic Computing based In-PCRAM              |     |

| Accelerator for CNN Processing                                                        | 60  |

| 9.1 Motivation                                                                        | 60  |

| 9.2 Challenges                                                                        | 60  |

| 9.3 Idea                                                                              | 60  |

| 9.4 Aim of this work                                                                  | 61  |

|                                                                                       |     |

| Chapter 10 <u>Future Direction 3</u> : In-DRAM BtoS Conversion with Variable Paramet- | (2) |

| ric Precision for Improving the Performance of CNN Applications                       | 63  |

| 10.1 Motivation                                                                       | 63  |

| 10.2 Idea                                                                             | 63  |

| Bibliography                                                                          | 65  |

| Vita                                                                                  | 75  |

## LIST OF FIGURES

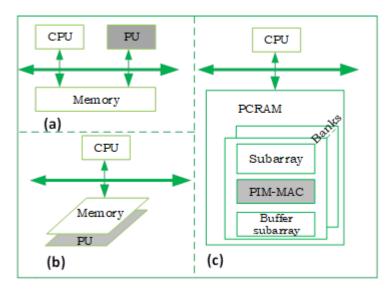

| 2.1<br>2.2        | Four major types of layers found in Convolutional Neural Networks (CNNs) [1].<br>a) Generic computer architecture b) Generic PIM approach to implement pro-<br>cessing unit inside main memory c) Proposed design framework for PCRAM-<br>based PIM implementation (can also be implemented in DRAM)                                  | 4<br>6         |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

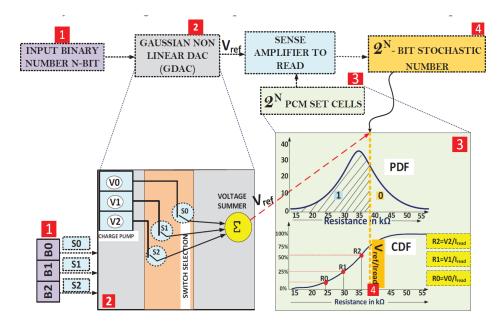

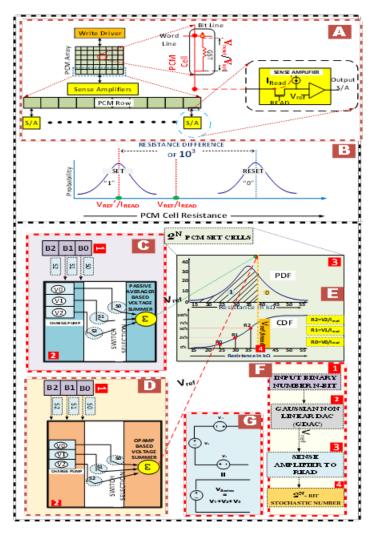

| 3.1               | Functional block-diagram of our proposed Phase Change Memory (PCM) based<br>Stochastic Number Generator (SNG).                                                                                                                                                                                                                        | 13             |

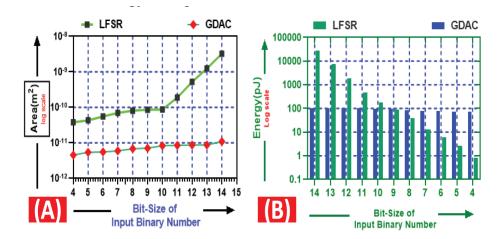

| 3.2               | (A) Area and (B) energy consumption values of our GDACbased SNG and conventional LFSR-based SNG for various bit-sizes of input binary number                                                                                                                                                                                          | 14             |

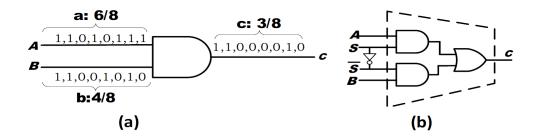

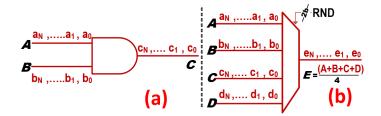

| 4.1<br>4.2        | Four major types of layers found in Convolutional Neural Networks (CNNs) [1].<br>Stochastic arithmetic circuits. (a) Multiplier (AND gate), (b) Adder (MUX                                                                                                                                                                            | 18             |

| 4.3<br>4.4        | circuit)                                                                                                                                                                                                                                                                                                                              | 19<br>20<br>21 |

| 4.5               | PCRAM activity flows for ODIN PIMC commands (a)B_TO_S, (b) CNN_MUL, (c) CNN_MUL, (d) S_TO_B, and (e)CNN_POOL.                                                                                                                                                                                                                         | 22             |

| 4.6               | (a) Execution time and (b) energy consumption for ODIN and other considered CNN processing systems, across VGG-1/2 and CNN-1/2 topologies                                                                                                                                                                                             | 26             |

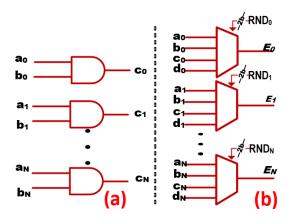

| 5.1               | Bit-serial rate-coded unary (stochastic) computing circuits for (a) multiplication (AND gate), (b) scaled accumulation (MUX).                                                                                                                                                                                                         | 31             |

| 5.2               | Bit-parallel rate-coded unary (stochastic) computing circuits for (a) multiplica-<br>tion (array of AND gates), (b) scaled accumulation (array of MUXs). Here, the<br>individual N bits of operands A, B, C, and D from Fig 6.1 are striped across N<br>copies of AND gates and MUXs                                                  | 31             |

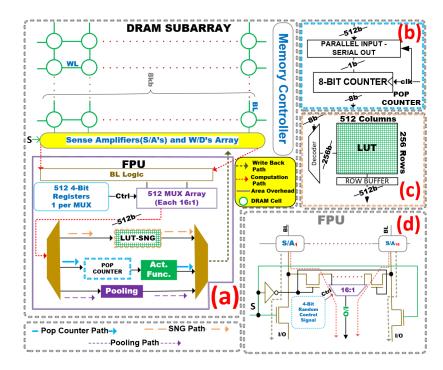

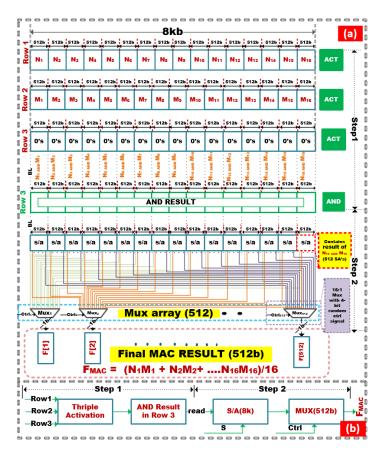

| 5.3<br>5.4        | The hierarchical structure of our ATRIA accelerator chip                                                                                                                                                                                                                                                                              | 32             |

| 5.5               | as part of the FPU                                                                                                                                                                                                                                                                                                                    | 33             |

| 5.6               | multiply-accumulate (MAC) function ( $F_{MAC}$ )                                                                                                                                                                                                                                                                                      | 35             |

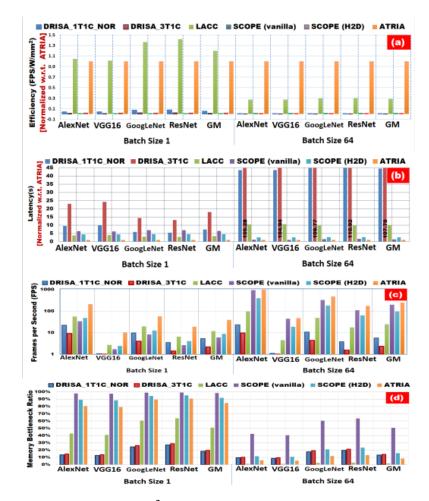

|                   | GM means geometric mean.                                                                                                                                                                                                                                                                                                              | 40             |

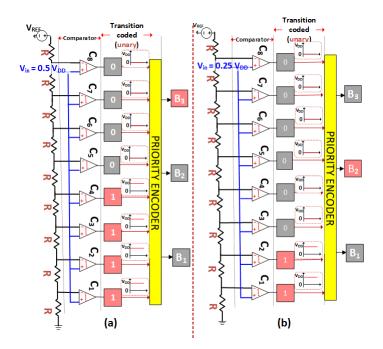

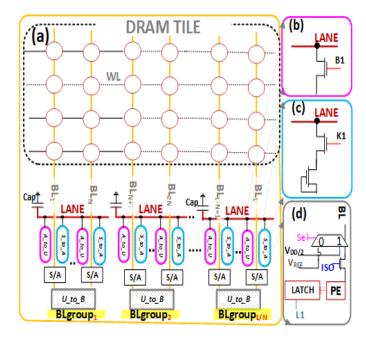

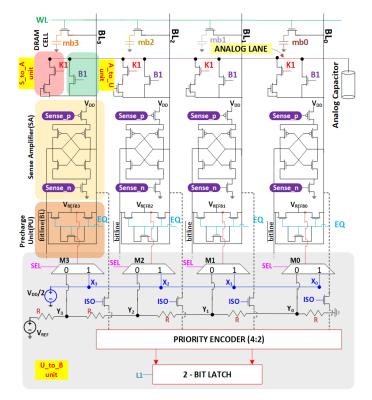

| 6.1<br>6.2<br>6.3 | (a) rate coded unary representation, (b) transition coded unary representation .<br>Flash ADC with a) Input $V_{in} = 0.5V_{DD}$ , and b) Input $V_{in} = 0.25V_{DD}$<br>Schematic layout of AGNI substrate and employed peripherals. Illustration of<br>(a) an AGNI-modified DRAM tile, (b) an A_to_U peripheral unit, (c) an S_to_A | 44<br>45       |

|                   | peripheral unit, and (d) a U_to_B peripheral unit. $\dots \dots \dots$                                                                                                                                                                | 46             |

| 6.4  | Schematic of AGNI StoB substrate with $N = 4$ and $BN = 2$ . Consisting of         |    |

|------|------------------------------------------------------------------------------------|----|

|      | peripheral structures S_to_A units, A_to_U units and U_to_B unit                   | 47 |

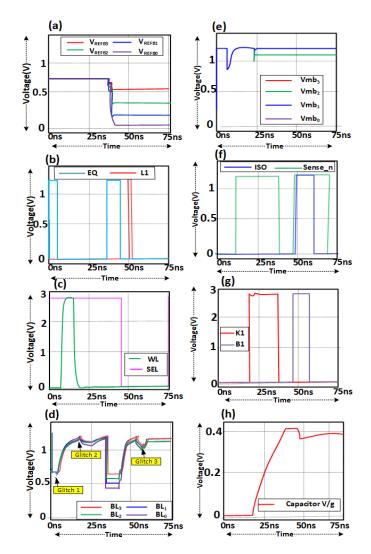

| 6.5  | SPICE simulation for AGNI StoB substrate with $N = 4$ . a)voltages of the          |    |

|      | precharge units $(V_{REF})$ b)Equalizer (EQ) and Latching signals(L1), c) Wordline |    |

|      | (WL) and SEL signals, d)Bitline (BL) voltages e)DRAM cell capacitor voltage,       |    |

|      | f) sense_n and isolation signal, g) charging (K1) and discharging (B1), and h)     |    |

|      | capacitor voltage                                                                  | 50 |

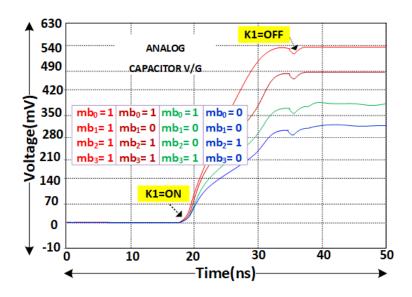

| 6.6  | Analog capacitor voltage at different number of 1's for 4 bit SN                   | 51 |

| 8.1  | Resistance Drift and broadening in the PCRAM row for SET and RESET state.          | 57 |

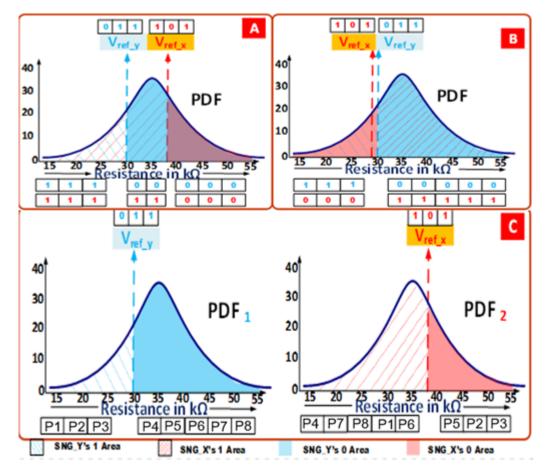

| 8.2  | Illustration of (A) PCRAM cell array, and (B) PCRAM resistance distributions       |    |

|      | for SET and RESET cells. (C) block diagram of CAPSTONE PCRAM-based                 |    |

|      | GDAC SNG without opamp-summer circuit. (D) block diagram of PCRAM-                 |    |

|      | based GDAC SNG [11] (E) PDF and CDF voltage mapping of $2^N$ PCRAM                 |    |

|      |                                                                                    | 58 |

| 8.3  | Correlation Manipulation: (A) positive correlation manipulation, (B)Negative       |    |

| 0.0  | correlation, and (C) uncorrelated                                                  | 59 |

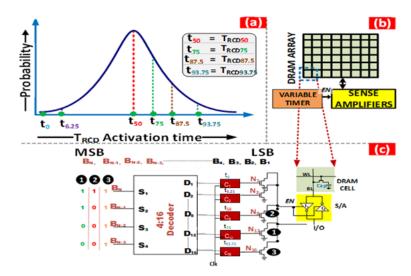

| 10.1 | (a) Gaussian distribution of DRAM $T_{RCD}$ activation time, b) DRAM peripheral    |    |

|      | connection with addon logic variable timer, (c) enlarged portion of the variable   |    |

|      | timer with enabled connection to the sense amplifier.                              | 63 |

|      | and the charter connection to the sense unprinter.                                 | 00 |

## LIST OF TABLES

| 2.1 | Advantages and disadvantages of SC                                                                                                                                                                                        | 8  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | The literature survey on PIM for arithmetic and logic operation with different memory class                                                                                                                               | 10 |

| 4.1 | : Required number of PCRAM reads, writes, and resultant total latency values for various ODIN PIMC commands.                                                                                                              | 25 |

| 4.2 | Requirement of memory capacity, number of PCRAM reads and writes for implementing various CNN topologies on ODIN accel-erator.                                                                                            | 25 |

| 4.3 | ANN benchmark topologies [2].                                                                                                                                                                                             | 27 |

| 4.4 | Area, energy and delay values for various add-on logic circuits for ODIN (scaled for 14pm CMOS)                                                                                                                           | 27 |

| 4.5 | for 14nm CMOS)                                                                                                                                                                                                            | 21 |

|     | implementing various CNN topologies on ODIN accel-erator.                                                                                                                                                                 | 27 |

| 5.1 | Latency, energy, and area overhead values of various hardware components of the FPUs in the PEs of ATRIA.                                                                                                                 | 37 |

| 5.2 | Average APE ( $\mu$ APE), standard deviation in APE ( $\sigma$ APE) and CNN testing                                                                                                                                       |    |

| 5.3 | accuracy (A) for SCOPE-Vanilla, SCOPE-H2D and ATRIA for various CNNs<br>Comparison of various accelerators with ATRIA, in terms of number of PEs (#PEs) and latency of MUL, ACC, MAC, binary to stochastic conversion (B- | 38 |

|     | to-S), and pop count (PC) operations.                                                                                                                                                                                     | 39 |

| 6.1 | Definitions and uses of various timing signals employed by AGNI substrate                                                                                                                                                 | 48 |

| 6.2 | Toggle time stamps ( $\uparrow$ or $\downarrow$ ) for various timing signals to realize the four operational steps of our AGNI substrate.                                                                                 | 48 |

| 6.3 | MAE, MAPE, RMSE, and $V_{MAX}$ of AGNI at different BLgroups lengths (N).                                                                                                                                                 | -  |

| 6.4 | Charge pump area and power dissipation $\ldots \ldots \ldots$                                             |    |

| 6.5 | Comparison of EDP, and AREA of prior StoB designs (Parallel PC [3], Serial                                                                                                                                                |    |

|     | PC [4]), and AGNI                                                                                                                                                                                                         | 55 |

#### **Chapter 1 Introduction**

The advent of big data has transformed the way we use technology [5]. Smart gadgets and applications rely on massive datasets that require advanced algorithms like machine learning, deep learning, and neural networks to extract meaningful information. Convolutional neural networks (CNNs) have emerged as powerful tools for visual image analysis and are extensively used in many fields, including computer vision, speech recognition, and natural language processing. A detailed explanation of CNNs will be provided in Chapter 2.

However, the high computational demands of CNNs pose a significant challenge for traditional computing systems. The convolution and fully connected layers, which are essential to CNNs, consist of many multiply and accumulate (MAC) operations that are both computation and data-intensive (refer to Chapter 2). Traditional computing systems are not designed to handle this massive amount of data, leading to extravagant energy and latency costs. They are facing significant challenges in keeping up with the computational needs of modern CNN applications. Moreover, frequent data movements between and processing and memory cores of these systems also add substantial energy and latency costs while processing CNNs. In Chapter 2, we discuss in detail the drawbacks of traditional computing systems in the context of processing CNN applications.

To mitigate these issues, there is a pressing need for alternative computing systems that are simpler to realize and have low-overhead hardware organization, with increased energy efficiency for arithmetic operations. The envisioned alternative computing systems should also address the issue of performance degradation and enable faster processing of CNNs.

To that end, to address the challenge of frequent data movements in traditional von-Neumann architectures, researchers have proposed using the processing-in-memory (PIM) technique and near-data computing [6]. This work is concentrated on the PIM technique, wherein the memory units are instilled with some in-situ processing capabilities. Due to this, the required data movements reduce drastically, resulting in increased processing throughput, latency and energy consumption. However, designing PIM architectures have its own challenges. First, the fabrication cost involved in the hardware modifications to enable PIM inside traditional main memory should be minimized. Second, the hardware circuitry that powers PIM architectures should be energy- and area-efficient.

To address this hardware efficiency challenge, researchers have come up with alternative arithmetic options such as stochastic computing and approximate computing [7] [8] [6]. Our research focuses on implementing the computations required for processing CNNs in the stochastic domain. Stochastic arithmetic operations are simpler to implement and have less hardware footprint compared to binary computation. However, stochastic computing suffers from limitations, namely the high area and energy overheads, and low performance of conventional circuits used for binary to stochastic number conversion. We address these shortcomings to enable stochastic computing in PIM architectures.

This dissertation focuses on developing alternative computing systems for faster processing of CNNs with high energy efficiency. Specifically, we explore two types of CNN accelerators: volatile memory-based (i.e., DRAM-based) and phase-change memory (PCM)- based PIM designs. Our initial work involves designing a novel stochastic computing-based PIM framework for CNN acceleration using mature DRAM technology. This framework utilizes bit-parallel stochastic computing, as described in Chapter 5. To further enhance the performance of our DRAM-based PIM accelerators for CNNs, we propose a new isolatency stochastic-to-binary conversion substrate, which is detailed in Chapter 6. Further, one potential alternative to DRAM is PCM, which offers scalability and energy efficiency benefits. Considering the popularity of PCM technology, we extended our idea of using the stochastic computing-based acceleration of CNNs to realize a PCM-based PIM architecture. This architecture is explained in detail in Chapter 4. Furthermore, we also contributed to the development of a scalable stochastic number generator (SNG) using the inherent stochasticity of PCM. This is explained in Chapter 3.

The contributions of this report are enumerated in Section 1.1. The report outline is provided in Section 1.2.

#### 1.1 Contributions

This thesis report makes the following contributions.

## Scalable Stochastic Number Generator for Phase Change Memory (PCM) Based In-Memory Stochastic Processing

In this study, we present the design of a high-performance and low-area footprint SNG that utilizes the inherently stochastic nature of PCM. We demonstrate the effectiveness of our PCM-based SNG by implementing it for different binary input lengths and comparing it with state-of-the-art Linear Feedback Shift Register (LFSR)-based SNG designs. We also identify the workflow towards achieving SNG scalability with minimal hardware footprint and discuss the challenges and constraints associated with the PCM-based SNG design. In Chapter 3, we provide a detailed explanation of our proposed SNG's energy and areasaving, which are  $250 \times$  and  $300 \times$ , respectively, compared to conventional LFSR-based SNG designs at 14-bit binary input length.

## ODIN: A Bit-Parallel Stochastic Arithmetic-Based Accelerator for In-situ Neural Network Processing in Phase Change RAM

We introduce a new PIM engine, named ODIN, that combines the advantages of stochastic computing and PIM architecture to facilitate the low-overhead in-situ acceleration of essential CNN functions such as multiply-accumulate (MAC), nonlinear activation, and pooling. ODIN employs hybrid binary-stochastic bit-parallel arithmetic and Phase Change RAM (PCRAM) as the underlying memory technology to achieve energy-efficient computation.

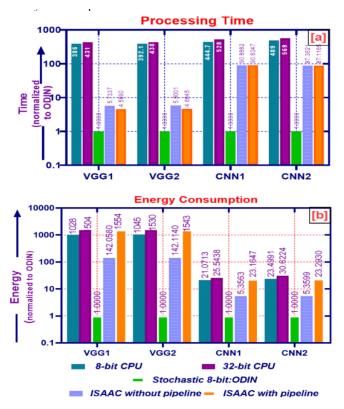

To assess ODIN's performance, we mapped four CNN benchmark applications on the proposed accelerator and compared it with a conventional processor-centric design and a crossbar-based in-situ CNN accelerator from prior research. Our analysis results indicate that the ODIN accelerator can achieve at least 5.8x faster and 23.2× more energy-efficient computation compared to the processor-centric design, and up to 90.8× faster and 1554×

more energy-efficient computation compared to the crossbar-based in-situ CNN accelerator from prior work. A detailed description of these findings is presented in Chapter 4.

## ATRIA: Low-latency, Energy-efficient In-DRAM CNN Acceleration With Bit-parallel Unary Computing

We introduce ATRIA, a novel in-DRAM accelerator that utilizes bit-parallel rate-coded unary computing for energy-efficient and high-speed inference of CNNs. ATRIA employs lightweight modifications to DRAM cell arrays to implement stochastic computing and accelerate MAC operations inside DRAM. By performing 16 MAC operations in only two consecutive memory operation cycles, *ATRIA* significantly enhances the latency, throughput, and efficiency of CNN inference processing. Chapter 5 provides a detailed explanation of these improvements.

# AGNI:In-situ, ISO-latency Stochastic-to-Binary Number Conversion for In-DRAM Deep Learning

Additionally, we present AGNI, a new technique for in-DRAM stochastic-to-binary number conversion for deep learning applications. AGNI makes minor modifications to existing DRAM peripherals and enhances the performance of existing in-DRAM stochastic-to-binary conversion circuits by reducing area, energy-delay product, and latency. Our SPICE simulations demonstrate that AGNI can achieve a  $3.9 \times$  improvement in performance across four deep CNN models. Chapter 6 provides a comprehensive explanation of AGNI and its simulation results.

#### **1.2 Report outline**

The report is thoughtfully structured to present a comprehensive account of our research work. In Chapter 1, we provide an introduction to the report, highlighting the motivation and objectives of our research. Chapter 2 offers a review of the existing literature and the required background.

We present our research contributions in Chapters 3, 4, 5, and Chapter 6, with each chapter focusing on a specific contribution of our research. Chapter 3 elaborates on our proposed workflow for a PCM-based SNG and discusses potential future work. Chapter 4 discusses ODIN, a stochastic MAC engine using PCM memory structure, along with our future plans for this research. Similarly, Chapter 5 focuses on ATRIA. In Chapter 6, we discuss our AGNI substrate.Finally, Chapter 7 concludes our report by summarizing our findings and contributions. We also highlight future scopes related to precision and correlation manipulation techniques to address stochastic inaccuracy in Chapter 8, Chapter 9, and Chapter 10.

Copyright<sup>©</sup> Supreeth Mysore Shivanandamurthy, 2023.

#### **Chapter 2 Background and Related Work**

#### 2.1 Convolution Neural Networks (CNNs)

In the present day, cloud computing and big data are very popular. It consists of an immense dataset to process and extract meaningful information. For applications, such as image recognition, computer vision, and other augmented reality-based technology, scholars found that convolution neural networks are a very favorable candidate and accelerated the growth of big data significantly. For our dissertation, we are focusing on the application related to the convolution neural network. Thus, it is necessary to give a brief overview of the generic CNNs, the structure of neural network layers, and the arithmetical operation involved in each neural network layer. Generally speaking, CNNs consist of four major types of layers, as shown in Figure 1, namely convolution (CONV), local response normalization (LRN), max pooling (POOL), and fully connected (FC) layers [9]. From all these layers, the major portion of information extraction of the input data takes place in the CONV and FC layers, where a very large number of MAC operations occur on the synaptic weights and input biases. These MAC operations typically involve many steps for intermediate value preparation and storage. Therefore, they can be highly time-consuming and energyconsuming. To give better insight, consider Equation 2.1, related to an FC layer, which consists of MAC operations between  $w_{i,j's}$  and  $a_{i's}$ .

Figure 2.1: Four major types of layers found in Convolutional Neural Networks (CNNs) [1].

Here in Equation 2.1,  $w_{i,j's}$  is the synaptic weight connecting ith node in layer 'a'to  $j^{th}$  node in layer 'b', and 'f' is a non-linear activation function (in our dissertation we use ReLU activation function).

$$\operatorname{out}(x, y)^{f_0} = \sum_{f_i=0}^{N_i} \sum_{k_x=0}^{K_x} \sum_{k_y=0}^{K_y} (w_{f_i, f_0}(k_x, k_y) \cdot \operatorname{in}(k_x, y + k_y)^{f_i})$$

(2.1)

#### 2.2 State of art machine learning technique

In this subsection, we are explaining the layers and NN's mathematical operations.

#### **Convolution layer**

This layer is used to identify the characteristic elements of input data. For example, see Figure 2.1. The filter is formed by  $K_x \times K_y$  coefficient kernel; these kernels are learned and form the synaptic weights for the next layer. The formula below shows the concrete method to find the output neuron at position (x, y) of output feature map  $f^0$ :

From the above Equation 2.2 input feature map fi can have multiple feature maps and the kernel is usually three dimensional i.e.,  $K_x \times K_y \times N_{if}$ .

$$out(x, y)^{f_0} = \max_{0 \le k_x \le K_x, 0 \le k_y \le K_y}$$

(2.2)

#### **Pooling layer (POOL)**

This layer computes the simple operation of max and average over the neighboring points. See Figure 2.1. Unlike convolutional or a classifier layer, a pooling layer has no learned synaptic weight and is represented as follows:

#### Local Response Normalization (LRN)

LRN implements the competition between multiple neurons at the same location. The function is like the lateral inhibition found in biological neurons. The impact of the LRN on the accuracy is negligible. Our work is not focused on implementing the LRN layers as evidenced by [10] [11] as shown in the below equation 2.3.

$$\operatorname{out}(j) = t\left(\sum_{i=0}^{N_i} w_{i,j} \cdot \operatorname{in}(i)\right)$$

(2.3)

#### **Classification layer**

Finally, the results of the sequence of Pooling, CONV, and LRN layers are fed to the classification layer. This layer is also called a fully connected layer. Check-in Figure 2.2, each  $N_i$  node is connected to output node No. The main function of this layer is to correlate the different features extracted from the filtering, pooling, and normalization to predict the output categories. Where  $w_{i,j}$  is the synaptic weights, t() is a transfer function. It can be tanh(x), max(0,x) and ReLU. Our research work considered the ReLU activation function as shown in equation 2.1.

#### 2.3 Processing in-memory (PIM)

#### Introduction

In this subchapter, we are going to discuss the conventional computer architecture and its drawback for big data applications. We also discuss the mitigation technique with the in-memory processing methodology especially using DRAM and NVM-based memory architecture.

#### Motivation

As explained in the earlier Section, CNN is being adopted by a wide spectrum of application domains such as natural language processing, image recognition, and computer vision. Nowadays, NN models employ increasingly enormous numbers of datasets and parameters. For example, Alexnet [12] [13] and VGG [14] are exercised in image classification with almost 61M and 138M parameters respectively. Keeping in mind this enormous data, the training of such a complex model demands enormous computation, memory resources, latency time, and energy. One critical aspect of this computation is the energy and large bandwidth requirement. These needs keep growing with the increase in parameters of dataset classification. But in present days the NN models are becoming deeper and larger; the data set and pressure on the faster runtime system need to keep growing. To mitigate this requirement, investigators come up with the low precision CNN model [15] and prune CNN [16], owing to the tradeoff in accuracy. Even these techniques try to improve the computation speed but have not addressed the key issue of CNN training model data migration requirement.

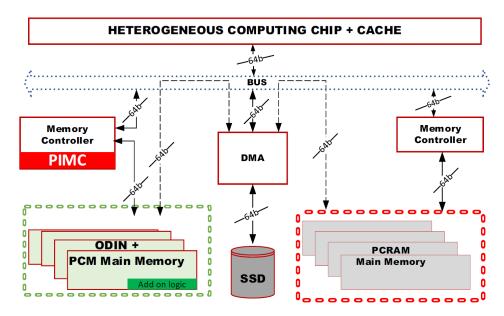

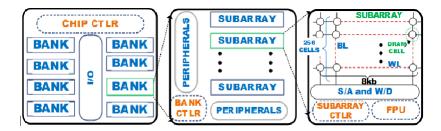

Figure 2.2: a) Generic computer architecture b) Generic PIM approach to implement processing unit inside main memory c) Proposed design framework for PCRAM-based PIM implementation (can also be implemented in DRAM).

#### Need of processing-in-memory computing

To address the data migration length challenges as explained before, researchers are considering the option of processing-in-memory technique (PIM). PIM is not a recent technique. It was actually proposed by IBM research in 2004, but most of the applications during previous years do not involve high data set volumes. One of the earliest PIM architecture examples is Stone's logic-based in-memory computer. Also, the cost of adding the extra circuitry (i.e., processing unit) inside the memory is not feasible due to the fabrication issues [17] [18]. However, big data with a conventional computer system (i.e., von-Neumann

architecture) is not able to suffice the system performance requirement. Thus, it is inevitable for today's digital world to incorporate the PIM architecture to meet the computing system requirements and accelerate the big data and cloud computing applications. There exist a few PIM architectures proposed by the researchers such as NON-VON [2], EXECUBE [19], Terasys [20], Computational RAM [21], and IRAM [22]. This architecture constitutes the add-on logic inside the DRAM to perform the addition operation in parallel. But many of these architectures were hindered by the setbacks/physical limitations of memory technology (i.e., DRAM) that prevents the integration of processing unit (PU) inside the memory.

#### New opportunity in modern memory

The researcher communities are of the opinion that the demand for large memory density by modern applications such as data learning with DRAM scaling has been pushed to their complete physical limits [23] [24]. It is becoming more problematic to increase the memory density [9] with reduced latency [25] [26] and improve the energy efficiency of DRAMbased memory architecture [27]. Consequentially, memory-related research companies are exploring the alternative to DRAM and also addressing the prior issues. Researchers have developed two solutions to overcome the limitations exhibited in prior memory systems for PIM implementation.

The first invention is the 3D stacked memory [18] [28]. In this technology, multiple layers of memory (in general DRAM) are stacked one above the other [29]. In addition to the multiple layers-based stacked 3D-DRAM memory architecture, the researchers have incorporated PU in one of the layers. Thus, the 3D-stacked-based technique reduces the data migration length thereby improving the system performance.

Second, researchers have found the major breakthrough of emerging non-volatile memory (NVM) can be a replacement for main memory subsystems. The main advantage of this NVM technology is the near-zero leakage current compared to the high leakage current in DRAM. Hence the NVM-based design exhibits better scalability and improves the memory density for data storage. The memory manufacturers are mainly considering three types of NVMs to replace the DRAM system at the main memory level:

- Phase change memory (PCM) [30]

- Magnetic RAM (MRAM) [31]

- Metal-oxide resistive RAM (RRAM) / memristor [32] [33]

All of the above mentioned NVM-based techniques are expected to provide the same memory latencies and energy consumption close to DRAM from literature studies. Furthermore, recent literature related to the NVM state [1] that the NVM is not only used for storing the data but can be used as the processing unit. In addition, each cell of NVM mimics the characteristics of a human neuron, which resemble the basic functionality of neural network character. Consequently, the hardware circuitry to implement the NN by using NVM-based memory technology can reduce the area requirement significantly. This idea attracted much research in PIM architecture using NVM-based systems. In addition,

| Features               | Advantages                                                          | Disadvanatages                                                                    |  |  |

|------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|

| Operating Speed        | short clock periodLong bit streamMassive ParallelismLong bit stream |                                                                                   |  |  |

| Result quality         | high error tolerance<br>progressive precision                       | Low precision<br>random number fluctuations<br>correlations included inaccuracies |  |  |

| Circuit size and power | Tiny arithmetic components                                          | More random number sources and stochastic to binary conversion ckts               |  |  |

| Design Issues          | Rich set of arithmetic components                                   | Little CAD tool support at present                                                |  |  |

Table 2.1: Advantages and disadvantages of SC

numerous PIM works related to the NVM-based cells are processed in recent times to perform Boolean logic operations [34] [35].

Some examples include deep learning (DL), artificial intelligence (AI), voice recognition etc., used in healthcare, data-science management, and statistical investigation. These applications consist of tremendous data information for processing. von-Neumann led to a lot of data migration from the main memory to the processor and the final processed information is stored back again in the main memory. From recent research studies, it is calculated that the data migration is 100× greater than the ADD operation [26] [20]. Also, this system suffers from memory-wall issues due to limited memory channel bandwidth for data transmission. To mitigate this drawback, we are reusing the concept of processing in-memory/compute-in-memory concepts [36] [37]. In PIM the processing unit is made closer or within the main memory causing reduced data migration length.

Consequently, this modification in PIM with reference to the baseline memory system leads to the enhanced performance of the computing system in multifold [38] [39] [40]. Processing in memory (PIM) is not a new research area. It was started in early 2004 [20] by IBM research members, but during that time the fabrication issue and high cost hindered the research progress. However, nowadays with technology's progression the fabrication cost have been drastically reduced. It is stable to fabricate a computing unit/processing unit inside the main memory.

#### Motivation

Traditionally, the main memory in recent computing systems uses DRAM. However, due to the scaling and reliability issue in DRAM, high leakage current caused the hindrance in development at the sub-nanometer regime of 22nm [9]. Also, a conventional volatile memory system (i.e., DRAM) suffers from repetitive refresh requirements to retain the data because the stored memory data in DRAM is volatile. To overcome these challenges in recent times, researchers have conducted many experiments to replace DRAM with non-volatile emerging memory (NVM) such as Phase change memory (PCM/PCRAM), spintronic devices, and magnetic tunnel junction devices [41] [42] [43]. In addition to this NVM (especially memristive devices) have near zero leakage current and, it is easy to scale the size even fabricated to 7nm by IBM research [43]. Also, the memristive devices mimic the character of a neuron network thus reducing the hardware required to a very large extent. To give an example, using the CMOS logic the gate requirement to implement

a single neuron node of NN is very high (22 transistors). In contrast, we can replace this with a single memristive cell for a great hardware footprint reduction.

#### Background

Multiply-accumulate (MAC) is the most widely used arithmetic operation, which is both a data and compute-intensive operation. In this chapter of our dissertation, we are concentrating on the PIM architecture in recent times to perform the MAC operation and use of data-intensive applications such as deep learning, convolution neural network, and relevant works.

PIM are classified based on the data interpretation and stored in the memory array into two classes. They are PIM-A [44] and PIM-P 54 [45]. First, consider some of the following applications that use the resistance changes to compute and transmit data, and output is produced in the memristive array called PIM-A [46]. Also, these PIM-A architectures such as Snider [38], IMPLY, and FBL [47], use the resistive changes as their input and output of the memristive crossbar. Further, hybrid PIM-Ah is proposed, which consists of resistive accumulator [46], and majority logic [48]. But these architectures suffer from the reliability issue of DAC and ADC components.

Second, in some PIM operations, the output is produced in the periphery of the memory unit as voltage changes and this class of architecture is called PIM-P. Depending on the voltage representation in PIM-P, memory systems are broadly classified into resistive PIM-Pr and PIM-Cr [25] [49]. Some of the recent CIM-Pr work is Pinatubo [50] [51], scouting [15], and HieIM [52] where the output peripherals are very simple and less complex to design. Whereas in PIM-Cr the output peripheral circuits are complex to design [53] [54]. One key point to be remembered is that PIM-Cr uses ADC/DAC units at the output to perform the calculation which consumes almost 85% of area and 90% of total energy consumption.

#### Work related to MAC operation

To maintain brevity and consistency, we narrow down our documentation related to the PIM-based accelerator with only arithmetic and arithmetic with logical operation accelerator for MAC operation. Related work is tabulated in Table 2.2. Also, some of the recent works related to the arithmetic operation using PIM architecture, such as 3D-DRAM to perform convolution operation proposed by Wang [55]. However, this hardware implementation cost (i.e., complex fabrication steps) is expensive with a complex arithmetic processing unit (PU). Ahead HMC-MAC [27], NeuralHMC [56] [18] are 3-D DRAM-based accelerators for increasing the MAC operations, but the processing unit (PU) design is a complex and expensive fabrication process to implement.

To perform the massive MAC operations in parallel for a neural network using DRAM, literature such as McDRAM [57], where the processing unit (PU) of MAC is placed close to the column decoder and it suffers from the area overhead issues and timing violation.

Few recent articles use the LUT-based MAC operation such as LAcc [58] [59], where each MAC operation is disintegrated into smaller units that decompose the multiplication operation size and LUT size. However, the accuracy is very low in LAcc architecture.

|                      |      |                        | Data           | Large        | In Memory         | In memory       |

|----------------------|------|------------------------|----------------|--------------|-------------------|-----------------|

| Technology           | year | Name                   | precision      | Data         | Bitwise op.       | large Data Op.  |

|                      |      |                        |                | Mapping      |                   |                 |

| DRAM-3D              | 2017 | wang [64]              | 16b            | Bit parallel | N/A               | MAC             |

| RERAM                | 2016 | chi [65]<br>prime      | 6b             | crossbar     | N/A               | MAC             |

| MRAM/RERAM           | 2017 | du [66]                | 8-bit          | Crossbar     | AND/OR/NOR        | ADD/MUL/MAC     |

| MCRAM AND PCM        | 2018 | mimi [67]              | BWNN/<br>8-bit | Bit-serial   | AND/XOR           | MAC             |

| THYRISTOR DEVICES    | 2018 | joonseopsim [68]/lupis | 6-bit          | Bit-parallel | AND/NOR/SHIFT     | ADD,MUL,MAC     |

| RRAM                 | 2018 | halwani [69]           | BCNN/Var Width | Bit-Parallel | AND/SHIFT/OR/NOT  | MAC/SHIFT       |

| CMOL                 | 2018 | madhav [70]            | 8-bit          | Bit-serial   | AND/NOR/SHIFT     | MAC             |

| RERAM                | 2018 | haiyu [71] / lergan    | 16-bit         | Crossbar     | AND/OR            | MAC             |

| RERAM                | 2019 | gupta [61] / nnpim     | 16-bit         | Crossbar     | AND/OR            | MAC             |

| RERAM                | 2019 | RAPID [72]             | 16-bit         | Crossbar     | AND/OR            | MAC             |

| RERAM                | 2019 | angizi [21] [73]       | 10-bit         | Crossbar     | AND/OR            | COMPARISION     |

| STT-MRAM             | 2019 | hao [41] /pj-axmt      | 8-bit          | Crossbar     | AND/OR            | MAC             |

| DRAM                 | 2020 | roy [74]               | 8-bit          | Bit-parallel | AND/OR            | MAC             |

| MCRAM/ PCM           | 2018 | xie [75]/ aim          | BCNN           | Crossbar     | XNOR              | N/A             |

| MEMRISTIVE CROSS BAR | 2016 | shafiee [10] / isaac   | 16-bit         | Crossbar     | N/A               | MAC             |

| RRAM                 | 2018 | chen [28]              | DCNN           | Crossbar     | N/A               | MAC             |

| MEMRISTIVE CROSS BAR | 2017 | ankit [26]/ respare    | Var. Width     | Crossbar     | AND/OR/NOT        | MAC             |

| SOT-MRAM             | 2017 | angizi [30] / imc      | 8-bit          | Bit-Parallel | AND/OR            | N/A             |

| SOT-MRAM             | 2018 | angizi [31]/ cmp-pim   | 8-bit          | Bit-Parallel | AND/OR            | COMPARISON      |

| NVM                  | 2018 | nihar [76]             | Var. Width     | Crossbar     | AND/OR/NOT        | MAC             |

| НМС                  | 2019 | chuhan [18]/ neuralhmc | 16-bit         | Bit-Parallel | AND/OR/NOT        | MAC             |

| SRAM                 | 2019 | gao [77] / tangram     | 16-bit         | Bit-Parallel | AND/OR/NOT        | MAC             |

| HMC DRAM             | 2018 | jeon [27]/ hmc-mac     | Var. Width     | Bit-Parallel | AND/OR/NOT        | MAC             |

| NANOWIRE WITH NVM    | 2017 | liu                    | Var. Width     | Bit-Parallel | AND/OR/NOT        | ADD, MUL        |

| RERAM                | 2018 | long [78]              | 10-bit         | Crossbar     | AND/OR            | MAC             |

| DRAM                 | 2018 | shin [79] / mcdram     | 6-bit          | Bit-Parallel | AND/OR/NOT        | ADD, MUL        |

| DRAM                 | 2019 | wang [60]              | BCNN           | Bit-Parallel | AND/OR/NOT        | MAC             |

| DRAM                 | 2019 | deng / LAcc            | 8-bit          | Crossbar     | XNOR              | N/A             |

| MEMRISTOR            | 2017 | john [10]              | 8-bit          | Crossbar     | NOR               | NOR/SHIFT       |

| SOT-MRAM             | 2017 | zhezhi [44]            | 8-bit          | Bit-Parallel | AND/OR            | MAC             |

| WIDE IO2 DRAM        | 2017 | lei [80] / xnor-pop    | BCNN           | Crossbar     | XNOR              | N/A             |

| SOT-MRAM             | 2018 | angizi [81] /imce      | 8-bit          | Bit-Parallel | AND/OR            | MAC             |

| STT-MRAM             | 2018 | jain [82]              | 8-bit          | Crossbar     | NOR               | NOR/SHIFT       |

| NANOWIRE SPINTRONICS | 2018 | angizi [81]            | BCNN           | Crossbar     | AND/NOR           | N/A             |

| RERAM                | 2018 | ammer [16]/imaging     | 8-bit          | Crossbar     | NOR               | NOR/SHIFT       |

| NVM                  | 2018 | said [83] [84]         | 16-bit         | Crossbar     | AND/NOR/NOT/SHIFT | MAC/COMPARISION |

| DRAM                 | 2018 | li [85] [86]/ scope    | 8-bit          | Bit-Parallel | AND/OR            | ADD/MULT(STOCH) |

| SOT-MRAM             | 2018 | angizi [87] [88]/ dima | 8-bit          | Bit-Parallel | AND/OR            | MAC/COMPARISION |

Table 2.2: The literature survey on PIM for arithmetic and logic operation with different memory class

Further, ReRAM-based crossbar memory-based PIM architecture for high performance and massive parallelism in PRIME [60], NNPIM [61] but it suffers from very high computation delay time for multiple sense amplifier (SA) operations. Further, in some of the recent work (i.e., ISAAC [10], DaDiano [62] [63] ) MAC operation will be processed in a dedicated subsidiary crossbar-based processing chip. Even though the operating speed is high the hardware cost of fabrication and energy dissipation due to the dedicated crossbar-based memristive circuit is almost 85%. Next, there exists ReRAM-based crossbar memory-based PIM architecture for high performance and massive parallelism, e.g., PRIME [60], NNPIM [61]. Still, it suffers from very high computation delay time for multiple sense amplifier operations. Further MAC operation based on dedicated chip in ISAAC [11], DaDiano [63]. These systems are called near-data computing. Even though the operating speed is high, the hardware cost of fabrication and energy dissipation due to the dedicated crossbar-based memristive circuit is almost 85%. Also, the dedicated chip will not incorporate the enormous data set of the current big CNN applications.

Researchers have tried to use the approximate computation technique to reduce the

hardware footprint with tradeoffs in accuracy, some of these works are Pj-AxMTJ [89]. LAcc [90]. Further, XNOR-POP [91] is used to reduce the arithmetic operation in the convolution neural network to implement BNN. This results in a reduction of complex arithmetic operations into simple logic operations. In this article, the author used the wide-IO DRAM to show the BNN implementation. Also, recent work by DIMA [87] converted all the computationally expensive components into simple logic circuits with better approximation. They have shown the feasibility by mapping the AddNet CNN application to SOT-MRAM-based memory architecture. Likewise, modification in sense amplifier performs the logical operation as shown in Pinatubo [92] to perform MAC operation used in CNN applications such as CiM-SCAM using FeFET and SRAM technology. SCOPE [93] uses SC to perform bulk bit-wise logic operations (Limited logic function), but the study is limited only to multiplication. This document can be used as a manual for future scope and improvement needed for PIM architecture with the class of device technology.

Chapter 3 Scalable Stochastic Number Generator for Phase Change Memory (PCM) based In-memory Stochastic Processing

#### 3.1 Chapter Overview

In this chapter, a novel approach to designing a Stochastic Number Generator (SNG) was proposed, which leverages the inherent stochastic nature of Phase Change Memory (PCM). The PCM-based SNG was implemented and tested for different binary input lengths, and its performance was compared to the state-of-the-art Linear Feedback Shift Register (LFSR)-based SNG. The proposed SNG was found to be highly scalable with a minimal hardware footprint, while also overcoming the challenges and constraints associated with the workflow of PCM-based SNG.

Overall, the proposed SNG was shown to offer significant improvements over conventional LFSR-based SNGs in terms of energy and area savings, with up to  $250 \times$  and  $300 \times$  improvements, respectively, for a 14-bit binary input length. These results demonstrate the potential of PCM-based SNGs as a promising solution for stochastic arithmetic-based CNN accelerators.

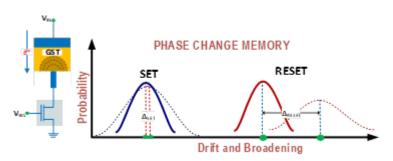

#### 3.2 Background: Phase change memory

A PCM cell embeds a small volume of chalcogenide material  $Ge_2Sb_2Te_5$  (GST) [94], which can be programmed into two different states (i.e., crystalline/SET state and amorphous/RESET state) with dramatically different electrical resistance [17]. The amorphous (RESET) state represents a binary "0", while the crystalline (SET) state represents a "1". The resistance of PCM cells in the SET state (RSET) follows a normal distribution in the  $k\Omega$  range [30], whereas the resistance of PCM cells in the RESET state (RRESET) follows a normal distribution in the  $M\Omega$  range [9], as shown in Figure 3.1-(B).

Typically, for a PCM array,  $I_{READ}$  and  $V_{REF}$  are judiciously designed such that  $V_{REF}/I_{READ}$  falls in between the resistance distributions of SET and RESET cells (Figure 3.1-(B)). As a result, for a PCM row being read,  $V_{SET}$  for all SET cells is less than  $V_{REF}$ , whereas  $V_{RESET}$  for all RESET cells is greater than  $V_{REF}$ , enabling the distinction of the SET cells (logic '1's) from the RESET cells (logic '0's) with 100% probability.

Now consider that a SET PCM row with all its cells pre-programmed in the SET state (storing '1's) is being read. For this read operation, if we can control  $V_{REF}$  such that  $V_{REF}/IREAD$  falls somewhere on the resistance distribution of the SET cells, we can control the number of cells that would be read as '1's. For example, if we can control  $V_{REF}$  to be  $V_{REF}$ ', as shown in Figure 3.1-(B),  $V'_{REF}/I_{READ}$  would fall at the center of the resistance distribution for SET cells. As a result, only 50% of the cells in the SET PCM row would be read as '1's (as these cells fall on the left of the  $V_{REF}'/I_{READ}$  reference), and the remaining 50% cells would be read as '0's. Learning from this observation, we leverage a judicious control of the PCM read operation to design an efficient SNG, as described next.

#### 3.3 Stochastic Number Generator

Figure 3.1 presents a functional block diagram of our proposed Stochastic number generator (SNG). In the field of Stochastic computing, we need to have, complete control on a total number of 1's and 0's and which is controlled by the voltage reference value  $(V_{REF})$ . Apart, from this Stochastic computing, we don't need a true random number generator (RNG) with uniform distribution. We only need to have an RNG that we can control the number of generated 1's in its output. To convert an N-bit input number (Figure 3.1-1) into a 2N-bit Stochastic bit-vector (Figure 3.1-4), our SNG employs a PCM-based Gaussian digital-to-analog converter (GDAC) (Figure 3.1-2) that provides  $V_{REF}$  for reading a row of 2N PCM cells (Figure 3.1-3) pre-programmed in the SET state. Figure 3.1-2 illustrates the GDAC operation for a 3-bit binary input (B2B1B0), which can be generalized to any N-bit binary input (BN-1..B1B0). In general, an N-bit GDAC contains N switches (S0 to SN-1), each of which corresponds to a bit (B0 to BN-1) in the N-bit input number and depending on the bit's value ('0' or '1'), connects its respective voltage source (V0 to VN-1 – implemented using charge pumps [93]) to the voltage summer circuit. We assume that the cumulative distribution function (CDF) for the resistance of PCM SET cells (Figure 3.1-3) is available at the design time. Therefore, the voltage level of the voltage source, corresponding to a bit BX from the N-bit input, can be determined at the design time as: VX =  $I_{READ}$  × CDF-1(2X/2N), where CDF-1 is the inverse CDF that gives the resistance value RX (Figure 3.1-3 and 3.1-4) for the given probability number. Accordingly, our proposed N-bit GDAC produces  $V_{REF}$  using the embedded voltage summer circuit (Figure 3.1-2). When this  $V_{REF}$  is used to read the PCM row with 2N SET cells (Figure 3.1 ), only the number of cells out of total 2N cells are read as '1's, and the remaining cells are read as '0's, thereby converting an N-bit input into a 2N-bit Stochastic output.

Figure 3.1: Functional block-diagram of our proposed Phase Change Memory (PCM) based Stochastic Number Generator (SNG).

For example, let us understand how this works for a 3-bit input number 101 (i.e., B2=1, B1=0, B0=1). To convert this number into a Stochastic number, our SNG should be able to produce a vector of total 8-bits with five '1's and three '0's. In our SNG (Figure 3.2), the voltage level V2 of the voltage source, corresponding to B2=1, can be evaluated as V2 = IREAD× CDF-122/23 = IREAD× CDF-14/8. Similarly, V1 and V0 can also be evaluated. Consequently, our proposed GDAC produces  $V_{REF}$  = B0V0+B1V1+B2V2 = V0+V1, as B1 is zero for our example number 101. This  $V_{REF}$  is used to read a total of  $2^3$  = 8 PCM SET cells and doing so results in only  $B_02_0 + B_12_1 + B_22_2 = 2^0 + 2^2 = 5$  cells to be read as '1's, and the remaining 3 cells to be read as '0's, hence, correctly converting the binary input 101 into an 8-bit Stochastic number.

#### 3.4 Results

We evaluated the area and energy consumption of our proposed SNG and compared the results with the LFSR-based conventional SNG from [25], for different bit-sizes of the input binary number from 4-bits to 14-bits. We used Cadence's Spectre for SPICE-level simulations of the LFSR-based conventional SNG and our GDAC-based SNG with the opamp-based voltage summer. We take the area, energy, and delay values for PCM from [30] and for charge-pump based voltage-sources from [95]. The  $\mu and\sigma$  for the SET resistance distribution for PCM cells are evaluated from [96] to be  $34.15k\Omega$  and  $6.54k\omega$ , respectively. Figure 3.1 and Figure 3.2, respectively, show the area consumption and energy values, for the two SNG designs, evaluated for 14nm technology by scaling the SPICE-based results for 45nm technology. From the figures, as the bit-size of the input binary increases from 4-bits to 14-bits, the energy and area values for our GDAC-based SNG hardly increase, compared to the exponential increase in the energy and area values for the conventional LFSR-based SNG. As a result, for a 14-bit input number, our GDAC-based SNG consumes  $300 \times$  less area and  $250 \times$  less energy, compared to the LFSR-based SNG.

Figure 3.2: (A) Area and (B) energy consumption values of our GDACbased SNG and conventional LFSR-based SNG for various bit-sizes of input binary number.

#### 3.5 Summary

In summary, the use of our PCM-based SNG for Stochastic PIM architectures provides the following benefits: (i) Our SNG can convert any N-bit binary number into a 2Y-bit Stochastic number, by simply using the  $V_{REF}$  generated by our GDAC to read total 2Y PCM SET cells. Here, Y can be any number  $\geq$  N, as an abundant number of PCM cells would already be available in PCM based PIM architectures, which provides an unprecedented opportunity to improve the precision of the generated Stochastic numbers without adding any significant conversion logic/circuit and related overheads in our designed SNG. (ii) As PCM SET cells are already available in a PCM-based PIM architecture, GDAC is the only block of our SNG that incurs area overhead. Moreover, unlike the LFSR-based SNGs from [25], our GDAC-based SNG can generate all 2Y bits of the output Stochastic number in parallel, which results in huge latency and energy savings for our GDAC-based SNG. In the future, we plan to evaluate the conversion-based and precision-based error efficiencies for our proposed SNG. Moreover, we intend to do a comprehensive comparative analysis of our proposed SNG with other SNG designs from prior work. Further, we will do detailed case studies to explore the utilization of our designed SNG for various Stochastic Processing-In-Memory (PIM) applications, including deep neural network inference and training applications.

## **Chapter 4 An Accelerator Based on Parallel SC for In-PCRAM Deep Learning Applications**

#### 4.1 Chapter Overview

This chapter proposes a new SC-based Processing-In Memory (PIM) engine called ODIN. ODIN is evaluated by mapping four CNN benchmark applications on it and is shown to be significantly faster and more energy-efficient than conventional designs and prior crossbar-based in-situ CNN accelerators. The proposed solution offers a promising approach to address the challenges associated with processing CNNs, and the ODIN accelerator has the potential to significantly improve the energy and time efficiency of CNN-based applications.

#### 4.2 Introduction

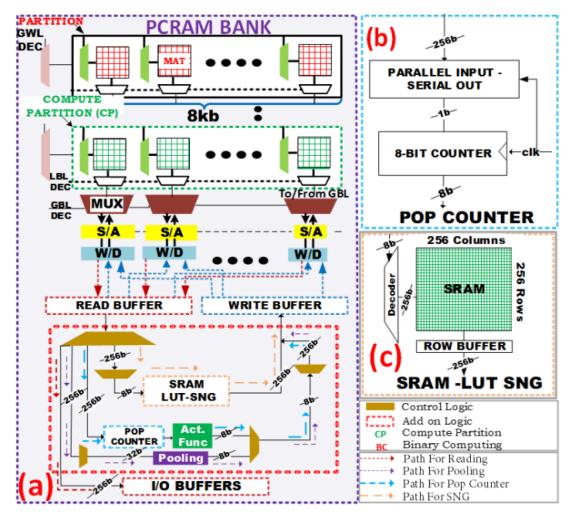

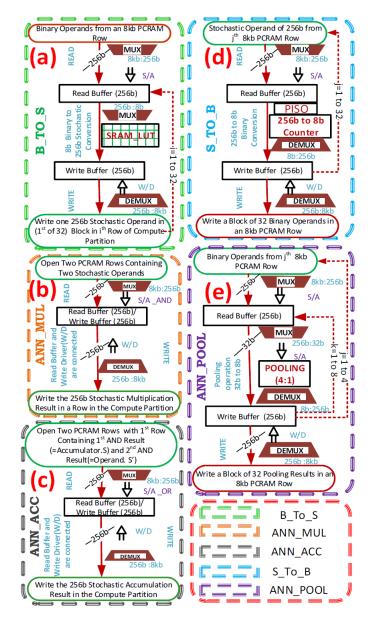

CNNs have achieved remarkable progress in recent years, and they are being aggressively utilized in real-world applications related to artificial intelligence (AI) and machine learning [47]. In general, CNNs mimic biological neural networks and utilize compute-heavy arithmetic functions such as multiply-accumulate (MAC), nonlinear activation, and pooling. Although these CNN functions are amenable to acceleration because of a high degree of compute parallelism, their acceleration is challenging because of the need to avoid the memory wall while accessing their large number of operands [9]. To address this problem, several prior works have explored crossbar memory-based processing-in-memory (PIM) accelerators (e.g., [9] [24]) that leverage the Kirchhoff's Law to perform MAC operations in the analog domain. However, such analog computing-based accelerators require powerhungry and sluggish digital-to-analog converters and analog-to-digital converters (DACs and ADCs), which diminishes the performance and energy-efficiency benefits of such accelerators. Moreover, these accelerators do not fully capitalize on the PIM paradigm, as they still have to heavily rely on conventional processor-centric computing for implementing essential CNN functions such as nonlinear activation and pooling. This motivates the need for simple, low-overhead, and energy-efficient in-situ accelerators that can realize the full potential of PIM-based CNN processing. In this chapter, we present a phase change RAM (PCRAM) based in-memory CNN accelerator called ODIN. ODIN uses Stochastic arithmetic to convert complex MAC operations into a series of simple and low-overhead in-situ logical operations that are implemented using the analog computing capabilities of PCRAM [94]. Stochastic arithmetic typically requires additional circuits to enable conversion of the operands between the Stochastic and binary number formats [23]. ODIN employs lightweight CMOS add-on logic inside PCRAM banks to implement such number conversion circuits with minimal area and power consumption overheads. ODIN also employs custom CMOS logic blocks to realize the binary arithmetic-based implementation of nonlinear activation and pooling functions of CNNs. Stochastic arithmetic for CNN processing has been utilized before in the DRAM-based in-situ accelerator described in [23]. The accelerator from [23] employs heavy add-on logic inside DRAM banks, which can increase the total area of DRAM chips by up to 4× [19]. In contrast, ODIN presents the first-of-a-kind Stochastic arithmetic-based accelerator that includes extremely low-overhead add-on logic and very lightweight modifications in PCRAM banks and PCRAM controller for efficient processing of CNNs. Our key contributions to this work are summarized below.

- We present a novel processing-in-memory (PIM) accelerator called ODIN that leverages hybrid binary-Stochastic arithmetic to accelerate CNN processing in PCRAM;

- ODIN employs low-overhead add-on logic and lightweight PCRAM modifications to implement Stochastic arithmetic based MAC operations and binary arithmetic-based activation and pooling operations directly inside PCRAM banks;

- We evaluate our ODIN accelerator for four CNN benchmark topologies (i.e., CNN1, CNN2, VGG1, and VGG2) from MLBench library [2], with two datasets MNIST and ImageNet;

- We compare the performance of our ODIN accelerator for the considered CNN benchmarks with the following architectures: baseline CPU-only with 32-bit floating precision, CPU-only with 8-bit fixed precision, as well as the pipelined and unpipelined variants of the ISAAC accelerator from [97].

## 4.3 Related work and motivation

Several processing-in-memory (PIM) based CNN accelerators are proposed in prior work (e.g., [97] [23] [10]- [2]). Some of these accelerators use memory in the conventional volatile RAM configuration (e.g., SRAM [14], DRAM [23] [10]- [13] based CNN accelerators), whereas some others use the emerging non-volatile memory in the crossbar configuration (e.g., STT-MRAM [17] [18], ReRAM [97] [15] [16] [2]). The RAM-configured CNN accelerators use bit-line computation to perform basic bit-parallel logical operations in a single read of a traditional RAM. Each memory column (bit-line) is further transformed into a bit-serial ALU by adding extra logic, multiplexing, and state elements in the peripheral circuitry, to perform complex arithmetic operations such as multiplication and addition, which are very essential for CNN processing [24] [1]. However, these accelerators incur high area-power overheads in their augmented peripherals and suffer from low throughput of bit-serial execution. Along the same line, a recently proposed DRAM-based in-situ accelerator [23] uses Stochastic arithmetic to perform CNN operations. However, this accelerator heavily modifies peripherals to facilitate logic circuitry, registers, and shifters to enable carry-save addition required for MAC processing. These modifications can result in up to  $4\times$  area increase per DRAM bank [19]. On the other hand, NVM crossbar-based accelerators also suffer from high overheads of ADC and DAC circuits. In contrast, our proposed design ODIN stands first of its kind to leverage the hybrid binary-Stochastic arithmetic inside PCRAM banks for implementing a very low-overhead acceleration of CNNs.