#### University of Kentucky

## **UKnowledge**

Theses and Dissertations--Electrical and Computer Engineering

**Electrical and Computer Engineering**

2022

## Development of DC Circuit Breakers for Medium-Voltage Electrified Transportation

Trevor Morgan Arvin University of Kentucky, arvintrevor@gmail.com Digital Object Identifier: https://doi.org/10.13023/etd.2022.118

Right click to open a feedback form in a new tab to let us know how this document benefits you.

#### **Recommended Citation**

Arvin, Trevor Morgan, "Development of DC Circuit Breakers for Medium-Voltage Electrified Transportation" (2022). *Theses and Dissertations--Electrical and Computer Engineering*. 180. https://uknowledge.uky.edu/ece\_etds/180

This Master's Thesis is brought to you for free and open access by the Electrical and Computer Engineering at UKnowledge. It has been accepted for inclusion in Theses and Dissertations--Electrical and Computer Engineering by an authorized administrator of UKnowledge. For more information, please contact UKnowledge@lsv.uky.edu.

### STUDENT AGREEMENT:

I represent that my thesis or dissertation and abstract are my original work. Proper attribution has been given to all outside sources. I understand that I am solely responsible for obtaining any needed copyright permissions. I have obtained needed written permission statement(s) from the owner(s) of each third-party copyrighted matter to be included in my work, allowing electronic distribution (if such use is not permitted by the fair use doctrine) which will be submitted to UKnowledge as Additional File.

I hereby grant to The University of Kentucky and its agents the irrevocable, non-exclusive, and royalty-free license to archive and make accessible my work in whole or in part in all forms of media, now or hereafter known. I agree that the document mentioned above may be made available immediately for worldwide access unless an embargo applies.

I retain all other ownership rights to the copyright of my work. I also retain the right to use in future works (such as articles or books) all or part of my work. I understand that I am free to register the copyright to my work.

### **REVIEW, APPROVAL AND ACCEPTANCE**

The document mentioned above has been reviewed and accepted by the student's advisor, on behalf of the advisory committee, and by the Director of Graduate Studies (DGS), on behalf of the program; we verify that this is the final, approved version of the student's thesis including all changes required by the advisory committee. The undersigned agree to abide by the statements above.

Trevor Morgan Arvin, Student Dr. JiangBiao He, Major Professor Dr. Daniel Lau, Director of Graduate Studies

## DEVELOPMENT OF DC CIRCUIT BREAKERS FOR MEDIUM-VOLTAGE ELECTRIFIED TRANSPORTATION

#### THESIS

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering in the College of Engineering at the University of Kentucky

By

Trevor M. Arvin

Lexington, Kentucky

Director: Dr. JiangBiao He

Department of Electrical and Computer Engineering

2022

Copyright<sup>©</sup> Trevor M. Arvin 2022

#### ABSTRACT OF THESIS

#### DEVELOPMENT OF DC CIRCUIT BREAKERS FOR MEDIUM-VOLTAGE ELECTRIFIED TRANSPORTATION

Medium-voltage DC (MVDC) distribution is an enabling technology for the electrification of transportation such as aircraft and shipboard. One main obstacle for DC distribution is the lack of adequate circuit fault protection. The challenges are due to the rapidly rising fault currents and absence of zero crossings in DC systems compared to AC counterparts. Existing DC breaker solutions lack comprehensive consideration of energy efficiency, power density, fault interruption speed, reliability, and implementation cost.

In this thesis, two circuit topologies of improved DC circuit breakers are developed: the resonant current source based hybrid DC breaker (RCS-HDCB) and the high temperature superconductor fault current limiter based solid state DC breaker (HTS-FCL-SSDCB). The RCS-HDCB utilizes a controllable resonant current source based upon wide bandgap (WBG) switches that enable low loss and fast fault interruption due to the fast switching speed. The voltage applied by the controllable resonant current source is much lower than the rated voltage of the DC breaker, allowing the utilization of significantly lower voltage rated WBG switches. The conduction path's sole component is a fast-actuating ultra-low resistance vacuum interrupter for high efficiency during normal operation. As the second DC breaker concept, the HTS-FCL-SSDCB is subdivided into a fault current limiter (FCL) and solid state DC breaker (SSDCB). The FCL is based upon a high temperature superconductor cable which has natural fault current limiting capabilities while having negligible insertion losses for normal load currents. The SSDCB utilizes WBG switches to decrease conduction losses compared to Silicon-based breakers. The FCL reduces fault current such that the number of semiconductive switches in the SSDCB is minimized. Both breakers feature a metal-oxide varistor device in parallel to clamp overvoltages and dissipate energy after fault interruption.

Modeling, simulation, and analysis in electrical and thermal domains are conducted to verify the functionality of the DC circuit breakers. The simulation results confirm the feasibility of these two DC breakers in their proposed applications of 2.4 kV electric aircraft and 20 kV shipboard MVDC distribution systems. KEYWORDS: Circuit breaker, MVDC, resonant current source, high temperature superconductor, fault current limiter

Trevor M. Arvin

May 6, 2022

# DEVELOPMENT OF DC CIRCUIT BREAKERS FOR MEDIUM-VOLTAGE ELECTRIFIED TRANSPORTATION

By

Trevor M. Arvin

Dr. JiangBiao He Director of Thesis

Dr. Daniel Lau Director of Graduate Studies

> May 6, 2022 Date

#### ACKNOWLEDGMENTS

I would like to formally thank the people whose support and encouragement allowed my personal work detailed in this thesis to come to fruition. Firstly, I would like to thank my advisor, Dr. JiangBiao He. His guidance and mentorship have been invaluable to me throughout my academic career. I would also like to express my gratitude to my thesis committee members, Dr. Aaron Cramer and Dr. Yuan Liao, for their valuable feedback on my work. Moreover, I am grateful for all the suggestions and support from Dr. Nathan Weise at Marquette University and Mr. Keith Waters at Schneider Electric. Many thanks to my friends and fellow labmates at AMPERE Lab. Their continuous motivation helped me immensely, and their dedication was a constant inspiration. Thank you to my friends, family, and loved ones for their constant support.

Finally, I would like to acknowledge the financial support received from the US Department of Energy Advanced Research Projects Agency-Energy (DOE ARPA-E) under award number DE-AR0001108 and the lead organization Marquette University on this project; the Development Fund Grants program with Southeastern Association of Electrical Engineering Department (SCEEE); and the Schneider Electric sponsored project under an undergraduate research fellowship.

## TABLE OF CONTENTS

| Acknowledgments                                                     |                                                      |            |  |  |  |

|---------------------------------------------------------------------|------------------------------------------------------|------------|--|--|--|

| List of Tables                                                      |                                                      |            |  |  |  |

| List of I                                                           | Figures                                              | vii        |  |  |  |

| Chapter                                                             | Chapter 1 Introduction                               |            |  |  |  |

| 1.1                                                                 |                                                      |            |  |  |  |

| 1.2                                                                 |                                                      |            |  |  |  |

| 1.3                                                                 | DC Circuit Breakers                                  | 5          |  |  |  |

|                                                                     | 1.3.1 Passive Resonant Mechanical DC Circuit Breaker | 8          |  |  |  |

|                                                                     | 1.3.2 Solid State DC Circuit Breaker                 | 9          |  |  |  |

|                                                                     |                                                      | 11         |  |  |  |

| 1.4                                                                 | *                                                    | 12         |  |  |  |

| 1.5                                                                 | 5                                                    | $12^{-1}$  |  |  |  |

| 1.6                                                                 |                                                      | 14         |  |  |  |

| 1.0                                                                 |                                                      | 11         |  |  |  |

| Chapter                                                             | 2 Resonant Current Source-Based Hybrid DC Breaker    | 15         |  |  |  |

| 2.1                                                                 | J                                                    | $15^{-5}$  |  |  |  |

|                                                                     | 1                                                    | 17         |  |  |  |

|                                                                     | 1 05                                                 | $18^{-1}$  |  |  |  |

|                                                                     |                                                      | $10 \\ 24$ |  |  |  |

| 2.2                                                                 |                                                      | $24 \\ 28$ |  |  |  |

| 2.2<br>2.3                                                          | 0                                                    |            |  |  |  |

| 2.3                                                                 | Conclusion                                           | 30         |  |  |  |

| Chapter                                                             | S .                                                  | 32         |  |  |  |

| 9.1                                                                 |                                                      |            |  |  |  |

| 3.1                                                                 | 0                                                    | 32         |  |  |  |

| 3.2                                                                 | 1 0                                                  | 34         |  |  |  |

| 2.2                                                                 |                                                      | 35         |  |  |  |

| 3.3                                                                 | 0 0 0                                                | 38         |  |  |  |

| 3.4                                                                 |                                                      | 42         |  |  |  |

|                                                                     | 3.4.1 Simulation Circuit                             | 42         |  |  |  |

|                                                                     | 3.4.2 2.4 kV Electric Aircraft Application           | 45         |  |  |  |

|                                                                     | 3.4.3 20 kV Electric Shipboard Application           | 49         |  |  |  |

| 3.5                                                                 | Conclusion                                           | 54         |  |  |  |

| Chapter 4 HTS Fault Current Limiter Based Solid State DC Breaker 55 |                                                      |            |  |  |  |

| 1                                                                   | 1                                                    |            |  |  |  |

| 4.1                                                                 | 1                                                    | 55<br>57   |  |  |  |

| 4.2                                                                 | 1 00                                                 | 57         |  |  |  |

| 4.3                                                                 | Operating Principle                                  | 58         |  |  |  |

| 4.4      | Conclusion                                             | 62 |

|----------|--------------------------------------------------------|----|

| Chapter  | 0                                                      |    |

|          | State DC Breaker                                       | 63 |

| 5.1      | SiC MOSFET Modeling                                    | 63 |

| 5.2      | High Temperature Superconductor Modeling               | 66 |

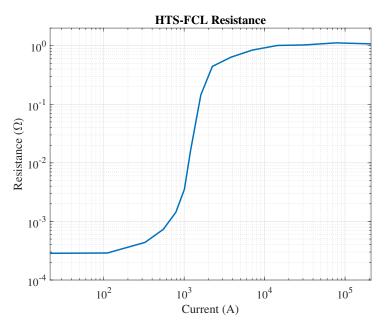

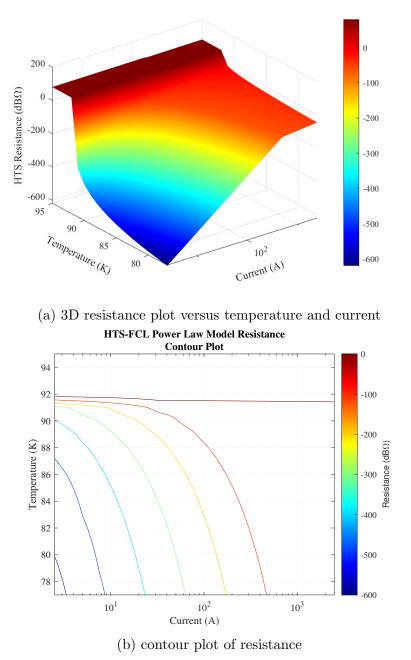

|          | 5.2.1 Resistance as a Function of Current              | 66 |

|          | 5.2.2 Power Law Model                                  | 68 |

| 5.3      | Transmission Line Lumped Parameter Model               | 70 |

| 5.4      | Simulation Results                                     | 72 |

| 0.4      | 5.4.1 Fault Interruption Simulation Results            | 73 |

|          | -                                                      |    |

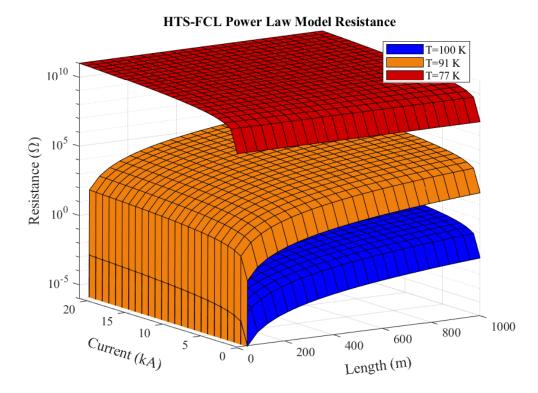

|          | 5.4.2 HTS Cable Power Law Model Sweep                  | 76 |

| 5.5      | Conclusion                                             | 79 |

| Chapter  | 6 Conclusion and Future Work                           | 82 |

| 6.1      | Conclusion                                             | 82 |

| 0        | 6.1.1 Resonant Current Source Hybrid DC Breaker        | 83 |

|          | 6.1.2 HTS Fault Current Limiter Solid State DC Breaker | 84 |

| 6.2      |                                                        | 86 |

| 0.2      | Future Work                                            |    |

|          | 6.2.1 Resonant Current Source Hybrid DC Breaker        | 86 |

|          | 6.2.2 HTS Fault Current Limiter Solid State DC Breaker | 87 |

| Bibliogr | aphy                                                   | 89 |

| Vita .   |                                                        | 94 |

## LIST OF TABLES

| Intended Applications of the RCS-HDCB                                                         | 17                                     |

|-----------------------------------------------------------------------------------------------|----------------------------------------|

| RCS Pulse Delay According to Reversals                                                        | 27                                     |

| Simulation Parameters of Schwarz Arc Model                                                    | 38                                     |

| Simulation Parameters of MOV IV Model for Aircraft System                                     | 42                                     |

| Simulation Parameters of SA IEEE Model for Shipboard System                                   | 42                                     |

| RCS Module Simulation Parameters                                                              | 44                                     |

| Circuit Parameters for RCS-HDCB Fault Interruption Simulation                                 | 45                                     |

| HTS-FCL Power Law Model Parameters                                                            | 70                                     |

| Transmission Line Simulation Model Parameters                                                 | 72                                     |

| HTS-FCL-SSDCB Fault Interruption Circuit Parameters                                           | 72                                     |

| Summary of Simulation Results for RCS-HDCB and HTS-FCL-SSDCB<br>MVDC Circuit Breaker Concepts | 83                                     |

|                                                                                               | RCS Pulse Delay According to Reversals |

## LIST OF FIGURES

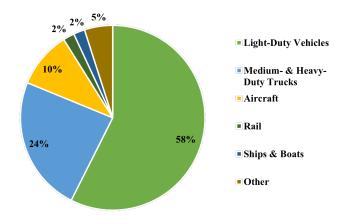

| 1.1 | U.S. transportation sector greenhouse gas emissions by source $\ . \ . \ .$ . | 2  |

|-----|-------------------------------------------------------------------------------|----|

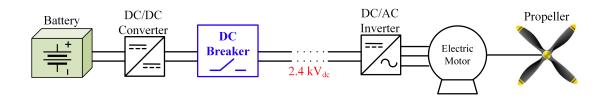

| 1.2 | General topology of an all-electric aircraft propulsion system                | 3  |

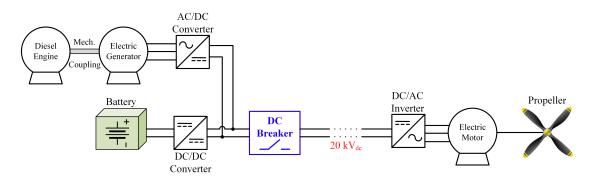

| 1.3 | General topology of a hybrid-electric shipboard propulsion system             | 4  |

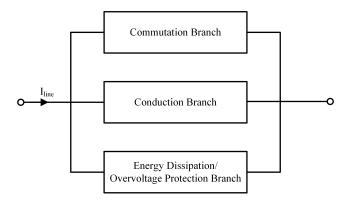

| 1.4 | Typical branches of a generic DC circuit breaker                              | 6  |

| 1.5 | Mechanical DC circuit breaker topology                                        | 9  |

| 1.6 | Solid state DC circuit breaker topology                                       | 10 |

| 1.7 | Conventional hybrid DC circuit breaker topology                               | 11 |

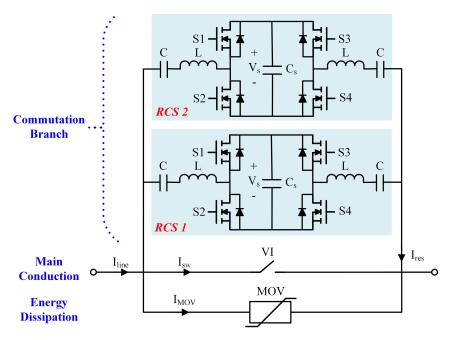

| 2.1 | High-level topology of the RCS-HDCB                                           | 16 |

| 2.2 | Circuit topology of the RCS-HDCB                                              | 18 |

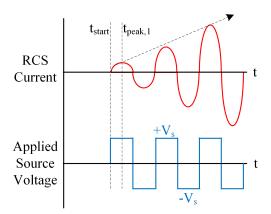

| 2.3 | Typical waveforms generated by RCS                                            | 19 |

| 2.4 | Typical control signals to generate resonant current in the RCS               | 27 |

| 2.5 | Equivalent RLC circuit of the RCS                                             | 28 |

| 2.6 | Transfer function of RLC network with different LC impedances                 | 29 |

| 2.7 | RCS reversal peak magnitude with different LC impedances                      | 30 |

| 3.1 | Generalized IV curve of MOV operating regions                                 | 39 |

| 3.2 | MOV and SA Models                                                             | 39 |

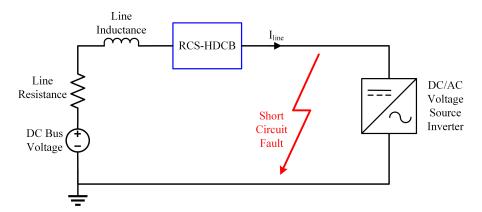

| 3.3 | High-level simulation circuit topology of RCS-HDCB                            | 43 |

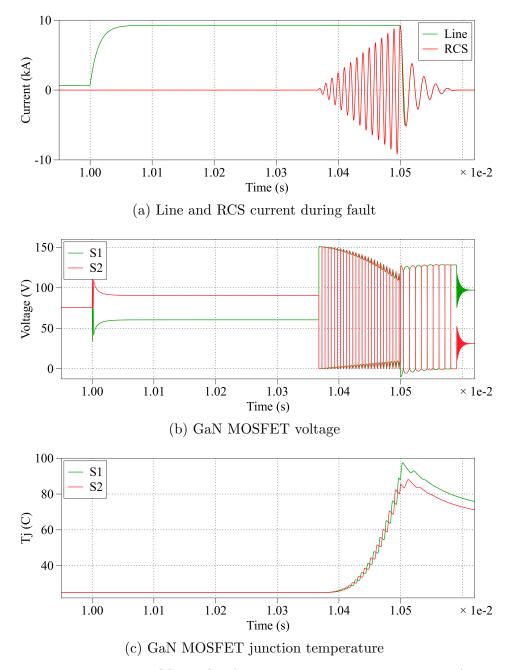

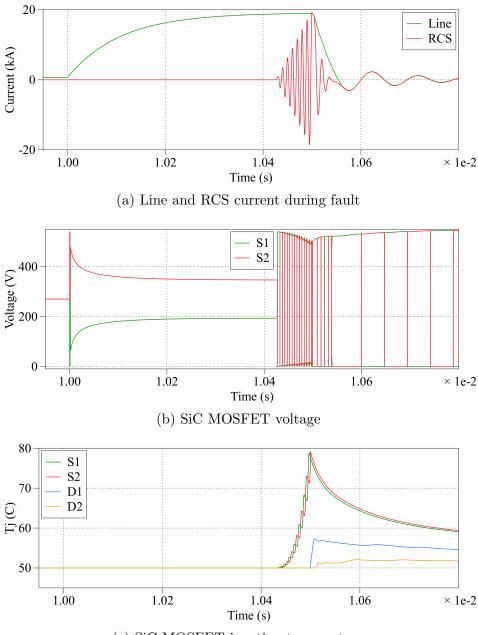

| 3.4 | 2.4 kV RCS-HDCB fault interruption operation waveforms                        | 46 |

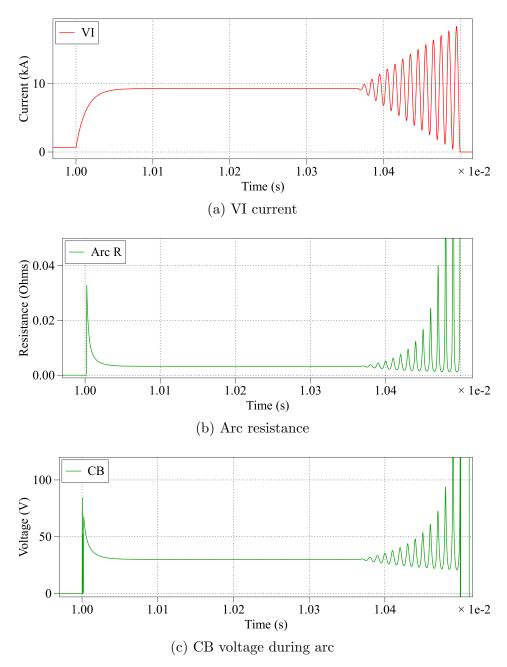

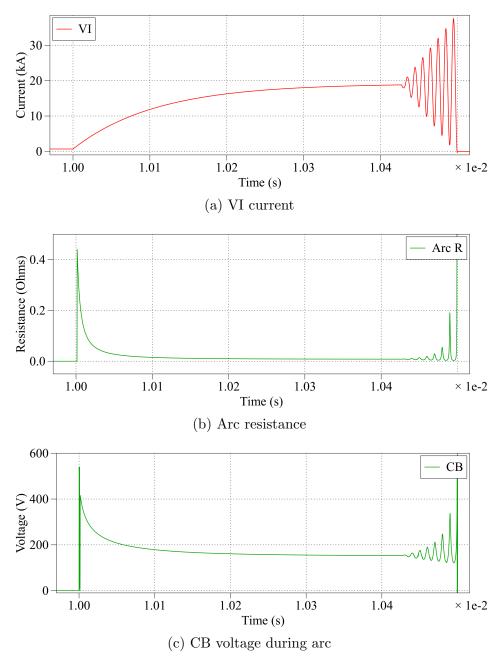

| 3.5 | 2.4 kV RCS-HDCB arc waveforms during fault                                    | 47 |

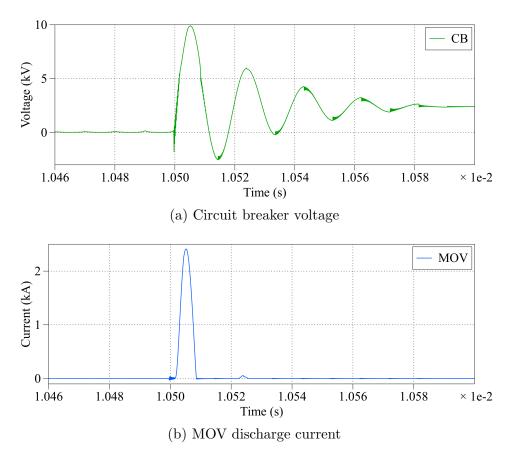

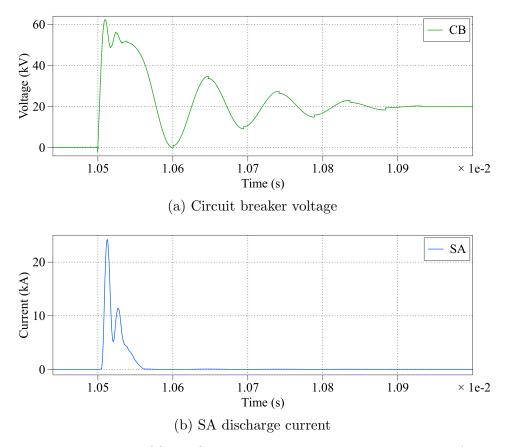

| 3.6 | 2.4 kV RCS-HDCB post-interruption overvoltage waveforms                       | 49 |

| 3.7 | 20 kV RCS-HDCB fault interruption operation waveforms                         | 50 |

| 3.8 | 20 kV RCS-HDCB arc waveforms during fault                                     | 51 |

| 3.9 | 20 kV RCS-HDCB post-interruption overvoltage waveforms                        | 52 |

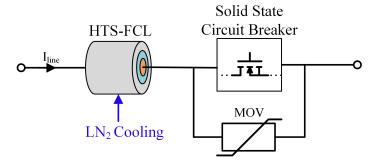

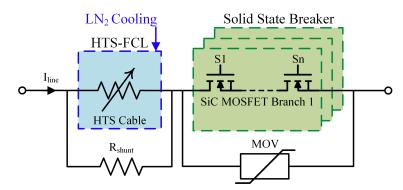

| 4.1 | High-level topology of HTS-FCL-SSDCB                                          | 56 |

| 4.2 | Detailed topology of HTS-FCL-SSDCB                                            | 57 |

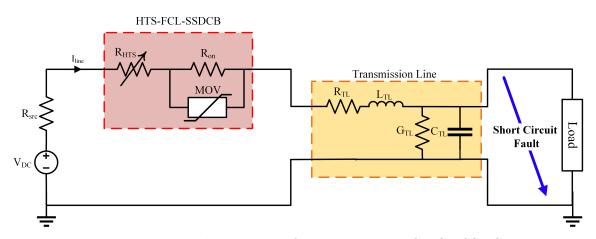

| 4.3 | Equivalent circuit of system with HTS-FCL-SSDCB                               | 58 |

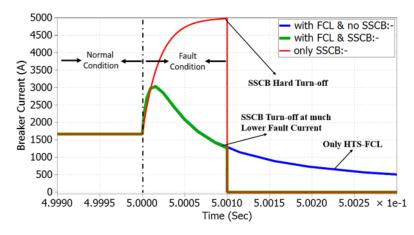

| 4.4 | Typical line current during a fault with and without FCL and SSDCB .          | 61 |

| 5.1 | Resistance curve of the variable resistance HTS-FCL model                     | 67 |

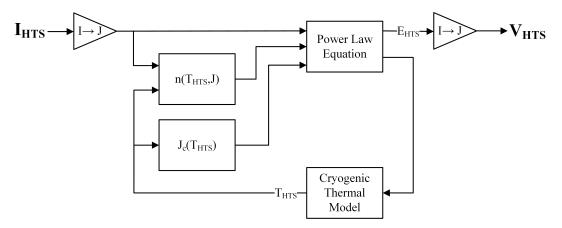

| 5.2 | Block diagram of a power law model for HTS cables                             | 68 |

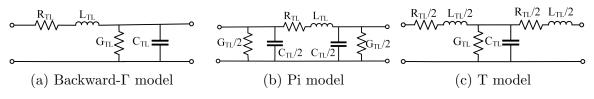

| 5.3 | Lumped parameter models of transmission lines in base units                   | 70 |

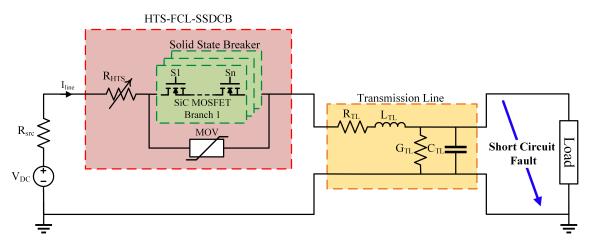

| 5.4 | Circuit schematic of HTS-FCL-SSDCB system for fault interruption              | 72 |

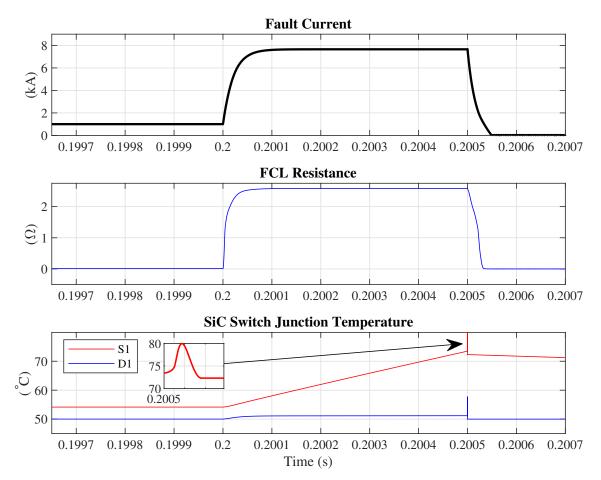

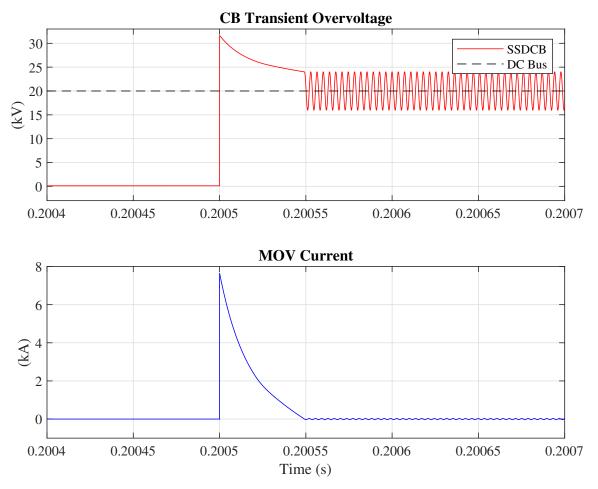

| 5.5 | Fault interruption waveforms of HTS-FCL-SSDCB from top to bottom:             |    |

|     | fault current, FCL resistance, and SiC MOSFET junction temperature .          | 74 |

| 5.6 | Overvoltage waveforms post-interruption of HTS-FCL-SSDCB from top             |    |

|     | to bottom: CB post-interruption voltage and MOV discharge current             | 76 |

| 5.7 | HTS-FCL power law model resistance sweep                                      | 77 |

| 5.8 | Resistance of HTS power law model versus length and current                   | 79 |

#### Chapter 1 Introduction

It has become clear that global climate change is becoming an increasingly pressing issue with each passing year. Humanity as a whole must work together across the scientific and political spectrum to combat our effect on the environment. That is why advancements in transportation, power generation and distribution must be made to do its part in curbing greenhouse gas emissions.

We have come to rely on fossil-fuel-based transport, but it accounts for a large amount of global emissions. These include vehicles such as the average automobile, aircraft, and ships. Transportation accounts for 29% of emissions in the United States [1] and 24% of emissions globally [2]. The emissions of these vehicles needs to be reduced to help curb the effects of global warming. This is the motivation in electrifying these vehicles to make hybridized and all-electric versions. These new vehicular systems need efficient and robust power distribution. Hybrid and electric automobiles are already being adopted in the market, but the development of electrified aircraft and shipboard is more challenging due to the much higher power ratings and complicated environmental operating environment. Referring to Fig. 1.1, aircraft and shipboard account for 12% of all transportation emissions in the United States. Emissions due to aircraft are especially harmful due to their deposition directly into the atmosphere [3]. The electrification of these modes of transport can help to drastically reduce their emissions. This presents new engineering challenges with the possibility of incorporating advanced electric technologies. Medium voltage DC (MVDC) distribution is one such promising technology for the enabling of electrified aircraft and shipboard, due to the advantages of low cable weight, high energy

Figure 1.1: U.S. transportation sector greenhouse gas emissions by source [1].

efficiency, and low cost [4–6]. However, the main limitation for widespread implementation of MVDC distribution is the lack of adequate circuit protection. Unlike AC systems, MVDC systems have higher short-circuit current resulting from the lower impedance, and there is no inherent zero crossing in the DC current to extinguish an arc. Thus, the conventional AC circuit breakers cannot be applied for DC systems. This thesis will be focused on developing MVDC circuit breakers (CB) that are fast, reliable, compact, and efficient for future electrified aircraft and shipboard applications.

#### 1.1 Research Motivation

MVDC systems have been proposed as a promising technology for future aircraft and shipboard systems. These systems can vary in degree of electrification such as moreelectric, hybrid, and all electric topologies. All of these topologies will be crucial in implementing more efficient, powerful, and environmentally friendly vehicles. Each requires robust fault protection since they are reliant on their electric distribution systems. MVDC has several advantages over conventional AC distribution. These include reductions in cable weight, system cost, eliminated need for synchronization, and increased efficiency (e.g., elimination of corona losses, fewer energy conversions, no reactive power transmission, etc.). For instance, AC distribution needs at least three cables to transmit all three phases. In DC, only two cables are needed for the positive and negative DC bus, and more power may be transmitted for the same cable crosssection [7]. This provides a crucial increase in system power density and efficiency that is pivotal in weight-critical transportation applications. The main technical barrier in the way of MVDC distribution is the lack of adequate circuit protection. The causes of difficulty in DC circuit protection is detailed in section 1.3.

#### **1.2** Electrified Propulsion Distribution Systems

DC distribution is best utilized in electrified propulsion due to the high efficiency and high power density. To enable this and allow for widespread implementation, fast and efficient circuit breakers must be developed. Any mode of transportation stands to benefit from electrification, but the work herein will focus on the higher-power applications of aircraft and shipboard.

The general propulsion topology of an electric aircraft is provided in Fig. 1.2. For simplicity, The exact topology depicted is an all-electric aircraft with a 2.4 kV DC bus, but other configurations are possible. The voltage of the battery is boosted with

Figure 1.2: General topology of an all-electric aircraft propulsion system

a DC/DC converter to a higher voltage for efficient distribution across the aircraft. This can be used to power many electrified systems. These systems can replace more complex and inefficient conventional mechanical systems, such as pneumatics or hydraulics [8]. In the figure, the DC breaker is shown installed on the 2.4 kV DC bus. If a fault were to happen between the DC circuit breaker and any of the electric loads (e.g., DC/AC inverter, wing de-icers, wing actuators, etc.), then the breaker would isolate the fault from the DC source before any damage could be done. This all-electric type is suited for short range commuter craft up to single-aisle aircraft. This is due to the lithium ion battery having a much lower power density than jet fuel and not being sufficient for long range flight. Larger aircraft with longer range can be developed if a jet fuel internal combustion engine were added to assist the stored battery energy (i.e., Hybrid electric). These could be in several different configurations such as more-electric, series, parallel, or series-parallel. These systems have shown good performance in reducing fuel burn and increasing efficiency. For instance, the Boeing 787 uses a more-electric topology to achieve a 20% reduction in fuel usage [5].

A hybrid-electric shipboard propulsion topology is provided in Fig. 1.3. Shipboard power ratings are generally higher than that of aircraft, so the battery storage can

Figure 1.3: General topology of a hybrid-electric shipboard propulsion system

be supplemented with diesel generators. While similar, the main difference between electrified aircraft and shipboard is the much higher DC bus voltage and higher power rating. In this instance, the DC bus can also be used to easily power electrified loads such as electric motors, rail guns, sonar, and more. Examples of such hybrid electric ships include the ABB hybrid ferry in the Norweigan fjords [9] and the commissioned ABB hybrid ferry in Maine [10, 11]. Both are plug-in hybrid ships, meaning that the battery storage can be pre-charged between voyages and the ship can choose between using electric energy or diesel engines. With this technology, the Maine ferry is expected to reduce up to 800 tons of carbon emissions yearly.

#### **1.3 DC Circuit Breakers**

In electric distribution, circuit breakers are the key components that protect the entire system from damage. If a short circuit fault occurs, then a large current that is orders of magnitude larger than rated load current will flow through the system. This could easily damage the power source and any sensitive components. For this reason, it is crucial to have adequate protection that is fast, efficient, and high power density.

In AC distribution, there are solutions that work well and provide full protection and fault isolation. Conventional mechanical circuit breakers are sufficient for AC systems. This is due to nature of AC voltages and currents. Since the system oscillates at a set frequency (e.g., 50 Hz, 60 Hz, or higher), then the inductance in the line is a significant choke that controls the speed at which fault current magnitudes increase. For mechanical circuit breakers during interruption operation, an arc will be established across its separating contacts due to the system inductance. Through this arc, the system current will continue to flow and the circuit cannot be isolated. If the current were to become zero, then the arc would quench, the separated contacts would build up their dielectric strength, and the circuit would achieve isolation. An AC system naturally has zero crossings twice every cycle (e.g., every 8.3 ms for 60 Hz), so there is no need to artificially induce a current zero. For these reasons, an AC circuit breaker can have an interruption speed on the order of several tens of milliseconds and provide sufficient circuit protection.

Contrasted to AC, DC current is much more difficult to interrupt. The distribution frequency is, ideally, zero. This means that the system's inductive impedance is minimized, so fault currents tend to increase in magnitude rapidly. Current is also constant in DC, so there is no natural zero crossing to extinguish arcs. This introduces the challenge of artificially inducing a current zero, and it is especially important for quenching arcs between mechanical contacts during interruption. For these reasons, it is critical to interrupt a DC fault within a few milliseconds [12].

The basic branch structure of a DC circuit breaker is provided in Fig. 1.4. Typically, DC breakers consist of three parallel branches. The conduction branch is the main branch, and all current flows through this during normal load conditions; all other branches are essentially open circuits in normal operation. Since no other branches are conducting at this time, the power losses of the conduction branch de-

Figure 1.4: Typical branches of a generic DC circuit breaker

termine the breaker's efficiency. The remaining branches are used only to assist in interruption. During a fault, the conduction branch starts to isolate (e.g., opening metallic contacts, shutting off devices, etc), and the commutation branch creates the current zero crossing in the conduction branch. This transfers the fault away from the conduction branch and into the commutation branch for a short while. This is usually accomplished by injecting current into the conduction branch or by providing a low resistance path for the fault current. This allows the conduction branch to achieve isolation. Since the system inductance is charged from the fault current, an overvoltage will be induced across the breaker upon the attempted current interruption. This is referred to as "inductive kick." The energy dissipation branch clamps this overvoltage such that it does not damage the breaker. In doing so, it also dissipates residual energy leftover in the system. Once completed, the fault has been cleared. Note that Fig. 1.4 displays typical branches. Some topologies have no need for these three distinct branches since one branch can perform a combination of functions. For example, a purely solid state breaker does not need a commutation branch since the solid state switches in the conduction branch are able to provide their own zero crossing. This will be explained in more detail in section 1.3.2.

In application, there is typically an additional mechanical breaker in series with the main DC circuit breaker. This extra breaker does not interrupt, but is simply a mechanical switch to provide total isolation and opens after the main breaker clears the fault.

On the other hand, it might be possible to design a power electronic converter such that it achieves fault tolerance. However, this is challenging and poses a risk when its microcontroller is tripped. This can happen if the circuit interfaces high electromagnetic interference (EMI). Considering the case of a basic two-level inverter driving an electric motor, if the controller gets tripped then the inverter will be out of control. Since the inverter now has no control signals, it cannot stop the motor. It will then continue to spin and act as an uncontrolled generator. The high back electromotive force (back-EMF) derived from the high-speed motor will be rectified through the inverter's antiparallel diodes and charge the DC bus to a high voltage. This highlights the need for a separate circuit breaker to protect the system in events such as this uncontrolled generator faults. The DC circuit breaker operates independently of the other components in the system. The breaker decides whether or not a fault has occurred typically based on the line current [13]. Then the breaker acts and separates the fault from the source protecting the system. In the following subsections, the pros and cons of the existing DC breaker technologies will be reviewed.

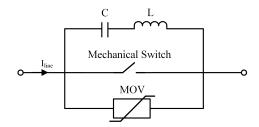

#### 1.3.1 Passive Resonant Mechanical DC Circuit Breaker

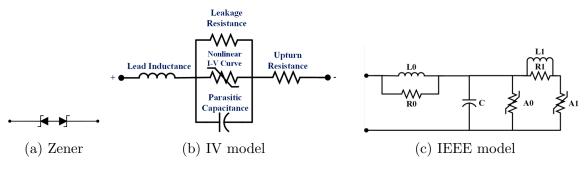

The topology of a passive resonant mechanical DC Breaker (PRMDCB) is shown in Fig. 1.5. This topology is most similar to the conventional circuit breakers used in AC distribution. The main conduction branch is comprised of a mechanical switch. Usually, this is a vacuum interrupter (VI) for MVDC systems, but it is possible to use other interrupting mediums such as sulfur hexaflouride. This branch is responsible for conducting all load current and creating an open circuit during a fault. Next, the commutation branch contains a passive LC resonating circuit. Once the mechanical switch starts to separate its contacts during a fault, an arc is established between them with a voltage drop. This voltage drop causes the LC resonant circuit to charge and oscillate at its resonant frequency. Once the peak oscillation is equivalent to the magnitude of the fault current, a current zero is achieved in the switch and the

Figure 1.5: Mechanical DC circuit breaker topology

arc quenches. Next the energy dissipation branch, a metal oxide variator (MOV), clamps the overvoltage and dissipates all residual energy. It should be noted that the MOV only conducts negligible leakage current until its knee voltage is surpassed by the induced overvoltage. At which point it becomes a very small resistance. This conducts the large fault current and clamps overvoltages. It is possible to use other devices in the energy dissipation branch, such as an RC snubber, but MOVs offer the best voltage protection comparatively.

Due to the mechanical switch being the sole component in the conduction branch, this breaker excels at efficiency. This is due to the ultra-low resistance of the mechanical contacts (e.g., approximately 1  $\mu\Omega$ ). However, the time needed to actuate the mechanical contacts results in poor interruption speeds on the order of 10-100 ms [14]. This is further exacerbated by the time needed to build up the resonating current in the passive LC circuit. The PRMDCB performs well in efficiency, simplicity, and cost, but the sluggish interruption speed makes this topology unsuitable to safely provide protection in DC applications.

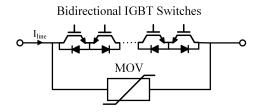

#### 1.3.2 Solid State DC Circuit Breaker

For faster interruption speeds, a solid state DC breaker (SSDCB) can be utilized. The topology of the SSDCB is given in Fig. 1.6. In the main conduction branch is a set of solid state semiconductor switches connected in series and parallel depending

Figure 1.6: Solid state DC circuit breaker topology

on the rated voltage and current requirements. These devices are traditionally silicon (Si) based such as insulated-gate bipolar transistors (IGBT) or thyristors. But recent advancements in wide bandgap semiconductor technologies allow the use of silicon carbide (SiC) or gallium nitride (GaN) metal-oxide-semiconductor field-effect transistors (MOSFET). Under normal load operation, these devices are held on and all load current flows through them. Notice that there is no need for a commutation branch in this circuit breaker. This is because the semiconductor devices do not generate an arc when they are switched off. In other words, the devices create their own zero crossing. Once the switches are off and have achieved current zero in the conduction branch, the MOV in the energy dissipation branch clamps the resulting overvoltage and dissipates residual energy.

The main benefit of the SSDCB is the ultra-fast interruption speed. Since the current is interrupted by simply turning off the semiconductors, the breaker can achieve a fault interruption speed within 100  $\mu$ s [15–17]. However, the semiconductor switches' on-state resistive losses result in relatively lower efficiency. They also need a cooling system to cope with the significant losses. These two problems are somewhat mitigated by opting for solid-state DC circuit breakers.

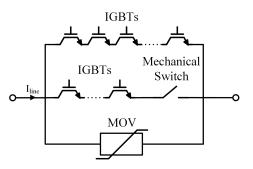

#### 1.3.3 Conventional Hybrid DC Circuit Breaker

The conventional hybrid DC breaker (HDCB) is a combination of the solid state and mechanical breakers. Its topology is provided in Fig. 1.7 [18]. The conduction branch is a combination of both semiconductor switches, usually IGBTs, and a mechanical switch. In doing so, the amount of IGBTs in the conduction path are reduced. Rated load current flows through this branch during normal operation. During a fault, the mechanical switch is commanded to open, and an arc is established that continues to conduct fault current. To achieve a current zero, the conduction path IGBTs are switched off while the commutation path is switched on. This provides a lower resistance path for the current to flow through, and the fault is redirected from the conduction path. This induces a current zero, and the arc between the mechanical contact quenches. Once the contacts have built up their dielectric strength, the commutation path can then switch off. At this point, the fault is interrupted and an overvoltage is induced across the breaker. This is clamped by the MOV in the energy dissipation branch and all energy leftover in the system is dissipated.

The HDCB is a compromise between the efficiency of the PRMDCB and the speed of the SSDCB. Since the IGBTs are paired with a mechanical switch in the conduction branch, the number of IGBTs needed in the path is reduced. The rated voltage is

Figure 1.7: Conventional hybrid DC circuit breaker topology

split between the mechanical switch and the IGBTs. The normal operation on-state resistance is then minimized resulting in higher efficiency than the SSDCB. Also, fastswitching IGBTs achieve zero current crossing much faster than the purely mechanical PRMDCB. However, the interruption speed is still limited by how quickly the actuator of the mechanical switch can open its contacts. Therefore, the interruption speed is on the order of several ms. The IGBTs are still present in the conduction path and have non-negligible losses that affect efficiency. The compromise is an improvement, but the interruption speed is too slow for DC systems and the efficiency is still undesirable due to the conduction path IGBTs.

#### 1.4 Objectives

This work's objective is to develop ultra-fast, efficient, compact, reliable, and lowcost circuit breakers that meet the needs of emerging MVDC distribution for electric aircraft and shipboard applications. Two breaker topologies will be studied: a resonant current source based hybrid breaker and a high temperature fault current limiter based solid state breaker. Both breakers will be designed by leveraging the advantages of the emerging wide bandgap switches, such as GaN and SiC MOSFETs, and will be electrically and thermally modeled and simulated to verify the function and feasibility of the two breakers.

#### 1.5 Outline of Thesis

The outline of this thesis is provided as follows:

Chapter 1 includes the necessary background on the motivation of MVDC distribution and its role in electrifying transportation. The concept of DC circuit breakers is introduced, and various common breaker topologies are reviewed. Chapter 2 introduces the resonant current source converter based DC circuit breaker. Its topology, RLC circuit, operating principle, and control scheme is detailed.

Chapter 3 includes the simulation models of the different subsystems of the resonant current source DC circuit breaker such as the resonant converter based on SiC MOSFETs, arc modeling for the VI, and metal oxide variator models. Simulation results are provided to confirm the function of the circuit breaker during fault interruption.

Chapter 4 details the concept of the high temperature superconductor fault current limiter based solid state DC breaker. An overview of high temperature superconductor technology and fault current limiter is provided along with the breaker topology and its operating principle.

Chapter 5 describes the simulation models used to simulate the high temperature superconductor fault current limiter based solid state breaker. Models include the SiC-based solid state breaker, high temperature superconductor cables, transmission line, and overvoltage mitigation. Simulation results are provided to demonstrate the effectiveness of the combination of fault current limiter with solid state breakers. A discussion is also given over the power law model for the high temperature superconductor cables.

The work is concluded in Chapter 6 to summarize the performance of the two breaker concepts based on the investigation presented in this thesis. Future work to further improve and verify the performance of these two DC circuit breakers is also discussed.

#### 1.6 Publications

Listed below are the journal and conference papers that were published based on the work to be introduced in this thesis, including:

- T. Arvin, J. He and N. Weise, "Modeling and Simulation of an Ultra-Fast Resonant DC Circuit Breaker Based on Current Source Module," Vol. 6 No. 1, Transactions on Techniques in STEM Education, Oct-Dec 2020.

- T. Arvin, J. He, N. Weise and T. Zhao, "Modeling and Simulation of a 20kV Ultra-Fast DC Circuit Breaker for Electric Shipboard Applications," 2020 IEEE Transportation Electrification Conference & Expo (ITEC), 2020, pp. 795-801.

- T. Arvin, J. He, and K. Waters "Solid-State DC Circuit Breaker Based on HTS Fault Current Limiter and SiC MOSFET Modules," accepted by 2022 IEEE Transportation Electrification Conference & Expo (ITEC), 2022.

Copyright<sup>©</sup> Trevor M. Arvin, 2022.

#### Chapter 2 Resonant Current Source-Based Hybrid DC Breaker

#### 2.1 Circuit Description

The conventional hybrid DC breaker (HDCB) is a compromise between the benefits and drawbacks of the solid state and mechanical breakers. The efficiency is improved over the solid state breakers, and the interruption speed is improved over the mechanical breakers. However, the losses are not negligible and the interruption speed is not sufficiently fast for DC protection. To improve upon the conventional HDCB, the semiconductors must be fully removed from the conduction path and the actuator opening the mechanical contacts must be improved. The efficiency can be increased by using a high frequency solid state resonant current source (RCS) in the commutation branch. This removes all semiconductors from the conduction path leaving only the contact resistance of the mechanical switch (in the range of  $\mu\Omega$ ). This eliminates their on-state losses during normal operation thus making losses negligible and efficiency high. Along with the high frequency RCS, the interruption speed is then improved by opening the mechanical contacts with a high speed actuator. In doing so, the breaker can interrupt faults much quicker than the conventional HDCB.

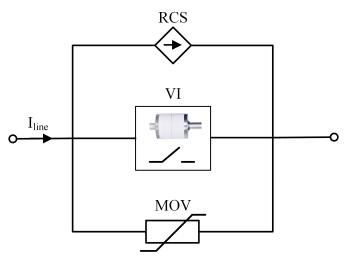

The high-level circuit topology of the resonant current source hybrid DC breaker (RCS-HDCB) is shown in Fig. 2.1. The sole component in the conduction branch is a vacuum interrupter (VI). This is operated by a fast-actuator that combines permanent magnets and Thomson coils to open the breaker within 500  $\mu$ s. The commutation branch is made of one or many RCS modules. The RCS-HDCB uses a modular approach such that the individual sub-systems can be stacked. This allows

Figure 2.1: High-level topology of the RCS-HDCB

for scalability to any DC power application. The RCS module itself uses low-loss fast-switching wide bandgap (WBG) devices to enable high frequencies of resonant current. Not only does this enable fast ramping of the resonant current, it enables physically smaller inductors and capacitors inside the RCS. The final branch is the energy dissipation branch. Much like other breakers, the RCS-HDCB uses a metal oxide varistor device to clamp overvoltages and dissipate residual energies.

The applications of this breaker are shown in Table 2.1. In one case study, the aircraft application [19, 20] will use GaN transistors due to the lower DC voltage level (i.e., 2.4 kV). In another case study, the shipboard breaker [21] will use SiC MOSFETs due to higher voltage level (i.e., 20 kV). These devices are used in lieu of conventional Si MOSFETs since they feature higher power density, lower switch losses, higher operating temperature capability, and faster switching speeds. This enables the RCS to have increased power density and achieve high frequencies of resonance with lower losses. For voltage protection, the aircraft application is able to use an off-the-shelf MOV since its voltage is relatively lower. However, a surge arrester (SA) (essentially many MOV disks) must be used for the shipboard application to

| Category           | Aircraft           | Shipboard          |

|--------------------|--------------------|--------------------|

| Rated Voltage      | 2.4 kV             | 20 kV              |

| Power              | 2.5 MW             | $20 \mathrm{MW}$   |

| Target Efficiency  | 99%                | 99%                |

| Interruption Speed | $\leq 500 \ \mu s$ | $\leq 500 \ \mu s$ |

| Lifetime           | 40k cycles, 35 yrs | 40k cycles, 35 yrs |

| Cooling            | Passive            | Passive            |

Table 2.1: Intended Applications of the RCS-HDCB

account for the increased voltage and system inductance.

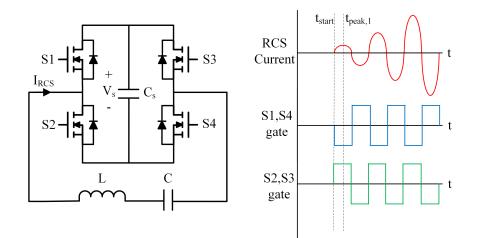

#### 2.1.1 Topology

The detailed topology of the RCS-HDCB is provided in Fig. 2.2. The main conduction branch is composed of a low-resistance VI. The energy absorption branch is composed of a MOV or a SA. The commutation branch either has a single RCS or multiple modules stacked. Stacking the modules in parallel increases the maximum fault current magnitude that the branch can safely commutate. For example, the two RCS modules in Fig. 2.2 effectively double the fault current capabilities without adding more stress on the individual modules. The modules themselves are H-bridge converters driving an LC resonator fed with a capacitor voltage source,  $C_s$ . The H-bridge oscillates its source voltage at the resonant frequency of the resonant inductors, L, and capacitors, C. This allows the building of resonant current and will be explained in more detail in Section 2.1.2. Low-voltage devices can be leveraged since the RCS source voltage is much lower than the DC bus voltage. This decreases the cost of each RCS module and allows them to be physically and electrically smaller. The main requirement is that the WBG devices must have high current carrying capabilities, especially pulse current, for fault commutation.

Figure 2.2: Circuit topology of the RCS-HDCB

#### 2.1.2 Operating principle

During normal operation, the nominal load current flows through the conduction path of the VI. Since the VI has extremely low contact resistance, the losses here can be neglected, enabling high energy efficiency. At this point, the RCS modules do not conduct and the MOV in the dissipation branch is a high impedance. Only negligible leakage current flows through the MOV, so both branches can be regarded as essentially open circuits. Once a fault occurs (i.e., the DC bus is shorted), an abnormally high current will flow through the conduction branch. This faulty current is orders of magnitudes higher than the nominal load current. Its rise time is limited by the line inductance and its magnitude by the line resistance. The fault is detected and the VI is commanded to open its contacts. This takes time to fully separate, and an arc is established between the contacts. It provides a low-resistance path for the current to continue to flow and will continue until the arc is quenched by a zero current. The main function of the commutation branch is to induce the current zero in the conduction branch. The current flowing through the conduction path is provided by equation 2.1.

$$i_{sw} = i_{line} - i_{res} \tag{2.1}$$

where:

-  $i_{sw}$ : conduction branch current

-  $i_{line}$ : line current

-  $i_{res}$ : commutation current

It is apparent from this equation that the current through the VI will be zero when the magnitude of the commutation current,  $i_{res}$ , is equivalent to the magnitude of the fault current,  $i_{line}$ . In doing so, an artificial zero crossing is achieved within the VI to quench the arc.

To induce the zero crossing, the RCS is controlled to build a fast-ramping oscillating current to oppose the fault current. An example of a typical RCS waveform is provided in Fig. 2.3. The WBG switches in the H-bridge are controlled to output a resonant current by oscillating the voltage from the pre-charged source capacitor,

Figure 2.3: Typical waveforms generated by RCS

$C_s$ , at the resonant frequency of the resonant inductors and capacitors. The resonant frequency is calculated by the Equation 2.2. It should be noted that the resistance of the RCS is determined by the parasitic or on-state resistances of the RCS components themselves. Resistance limits the peak resonant current of the RCS module and is thus desired to be minimal.

$$\omega_d = \sqrt{\frac{1}{LC} - \frac{R^2}{4L^2}} \tag{2.2}$$

$$\alpha = \frac{R}{2L} \tag{2.3}$$

where:

- $\omega_d$ : damped radian frequency (rad/s)

- L: equivalent inductance of RCS (H)

- C: equivalent capacitance of RCS (F)

- R: equivalent resistance of RCS ( $\Omega$ )

- $\alpha$ : damping constant

Once excited with alternating voltages, the resonant inductors and capacitors will create a ramping oscillating current that ramps approximately linearly with time. Each half period of resonance is referred to as a reversal since the resonating current alternates sign. Depending on the choice of source capacitance, resonant inductance and capacitance, and the on-state resistance of the WBG devices, the magnitude of the oscillating current will eventually saturate and decay at a high number of reversals. The choice of the source capacitor is the most significant in terms of saturation since it can only store certain amount of charge, so a sufficiently high capacitance must be chosen. It is preferable that the RCS achieves current zero within the linear growth portion of its current. Typically this is within a few tens of reversals. After many reversals, the current saturates, and there are diminished returns in the peak-to-peak current gain. The time at which the first peak RCS current occurs, and all subsequent, are given by Equations 2.4 - 2.5.

$$t_{peak,1} = \frac{1}{\omega_d} \arctan(\frac{\omega_d}{\alpha}) \tag{2.4}$$

$$t_{peak}(n) = (n-1)\frac{\pi}{\omega_d} + t_{peak,1}$$

(2.5)

where:

- $t_{peak,1}$ : 1st reversal peak (s)

- $t_{peak}(n)$ :  $n_{th}$  reversal peak (s)

- n: corresponding peak number

The magnitude of each of these resonant current peaks is given in Equation 2.6.

$$i_{peak}(n) = B(1)e^{-\alpha t_{peak,1}}\sin(\omega_d t_{peak,1})$$

(2.6)

$$B(n) = \frac{V_d(-1^{n-1}) - V_c(n-1)}{L\omega_d}$$

(2.7)

where:

- $i_{peak}(n)$ : magnitude of  $n_{th}$  reversal peak current (A)

- B(n): underdamped ringing coefficient

- $V_d$ : H-bridge's DC bus voltage (V)

- $V_c$ : initial capacitor voltage (V)

The current saturation is largely determined by the source capacitor, since the voltage across the capacitor will deplete over many reversals. The equations above

assume an ideal voltage source instead of a source capacitor, so the peak-to-peak current gain is not attenuated by the source capacitor's limited stored charge. With an ideal voltage source, the current saturation is controlled only by the impedance of the LC resonating circuit. Finally, the capacitor voltage stored at the end of each reversal is found by the Equation 2.8.

$$V_c(n) = \frac{B(n)}{C} \frac{\omega_d}{\alpha^2 + \omega_d^2} (e^{-\alpha \frac{\pi}{\omega_d}} + 1) + V_c(n-1)$$

(2.8)

where:

-  $V_c(n)$ : voltage stored in capacitor after the  $n_{th}$  reversal (V)

Larger magnitudes of commutation current can be achieved by either increasing the source voltage of the H-bridge or by utilizing more current reversals. Increasing the number of reversals in turn decreases the required initial source voltage of the H-bridge and vice versa. However, there is a limit to the amount of reversals possible. This is constrained by the rated voltage of the WBG devices, the rated current, and the saturation rate of the RCS. There is a tradeoff between the number of reversals and the peak junction temperature of the MOSFETs. Generally, the more reversals performed means a higher junction temperature. Using too few reversals would result in an initial source voltage that exceeds the voltage ratings of the MOSFETs. A low number of reversals would also drastically increase the peak-to-peak resonant current gain. This would put uneven wear on the WBG devices and have a high temperature differential per reversal. In doing so, it would negatively affect the reliability and lifetime of the RCS module.

Once the RCS module(s)' resonant current exceeds the magnitude of the VI current, the zero crossing is successfully achieved. This provides an opportunity for the arc to quench inside the VI. In doing so, the contacts become an open circuit and gradually rebuild their dielectric strength. The fault has now been interrupted, and the energy dissipation mode begins. The RCS module ceases resonance, and the fault current flows briefly through the resonant components and the anti-parallel diodes of the H-bridge. This serves the dual purpose of commutation and recharging the source capacitor. After interruption is completed, an overvoltage rapidly builds across the breaker due to the attempted interruption in the system inductance's current.

If the breaker did not have overvoltage protection, it would likely become damaged by the excessive voltage, or the arc could re-establish itself which would resume the fault. Since mechanical contacts are utilized and the WBG devices are decoupled from the full fault voltage, this topology is not as sensitive to overvoltages as others such as the SSDCB or conventional HDCB. The duty of the MOV or SA is to clamp this overvoltage such that it is within a safe limit for the breaker to endure. The MOV is an extremely nonlinear device. At relatively low voltage, the resistance is extremely large, but the resistance becomes extremely low for high voltages. This transition occurs at the knee voltage of the particular MOV device. In this low impedance state, the MOV clamps the overvoltage and dissipates the residual energy stored in the system impedance and resonant components of the H-bridge. The time it takes to expend the energy depends on the amount stored and the total impedance still present in the circuit. Once all leftover energy is dissipated, the voltage across the breaker relaxes to the nominal DC bus voltage of the distribution system, and the MOV resumes as a near-open circuit high impedance. At this point, the fault can be considered fully isolated.

Note that this design can handle bidirectional current in the systems. A positive or negative directed current can easily be detected by employing a current sensor in the main conduction path. The VI and MOV are naturally bidirectional, and the RCS can be utilized to compensate for whichever direction the fault current flows. By inverting the related pulse width modulated (PWM) signals, the pulsating commutation current can be reversed. This produces a negative or positive peak reversal for a correspondingly positive or negative fault current. In a simpler scenario, the RCS can instead utilize one extra reversal without the need to modify control signals. The current zero would then occur on the next reversal. Either approach can be used to provide interruption of bidirectional current. After the fault is interrupted, then the current would flow briefly through the antiparallel diodes of either S1 and S4 or S2 and S3, depending on its direction.

#### 2.1.3 Controls

The RCS components require an alternating voltage pulse in order to resonate charge between the inductor and capacitor. This builds a constantly ramping oscillating current through the RCS. Likewise, the oscillating of the RCS must be timed in tandem with the VI. If the RCS were to attempt current interruption before the VI contacts were fully open, it would be more likely for the arc to re-establish. This presents the danger of resuming the fault and failing interruption. Mechanical contacts have the greatest dielectric withstand capability when they are the farthest apart, so the peak reversal current must be timed at the moment when the VI is fully actuated.

Given a desired number of RCS reversals, the time at which the RCS must start resonating relative to when the VI starts to open can be calculated with Equation 2.9-2.10. This equation coordinates the peak reversal with the instance the mechanical contacts are fully open.

$$t_{res} = (m-1)\frac{\pi}{\omega_d} + \frac{1}{\omega_d}\arctan(\frac{\omega_d}{\alpha})$$

(2.9)

$$t_{start} = t_{VI} - t_{res} \tag{2.10}$$

where:

- $t_{res}$ : time to complete the desired number of reversals (s)

- $t_{start}$ : time delay to start RCS resonating after VI starts opening (s)

- $t_{VI}$ : time it takes to fully open VI (s)

- m: number of current reversals desired

The necessary source voltage to pre-charge  $C_s$  can be estimated using the Equations 2.11 - 2.15. Similar to the approach in [22], these equations use the envelope of the resonant current to calculate each peaks' magnitude. It works well for reasonable reversal numbers (e.g., within a few tens of reversals). In other words, the approximation is accurate enough for the linear region of resonant current growth but less so for the saturation region. This is derived via the provided equations, the RLC transfer function, and convenient assumptions about the shape of the source capacitor discharging voltage during interruption. The approximation tends to overestimate, so the voltage can be tuned exactly via a trial-and-error method in simulation, or a correction factor can be added given experimental testing.

$$Z_{LC} = \sqrt{\frac{L}{C}} \tag{2.11}$$

$$I_o = \frac{1}{Z_{LC}} \tag{2.12}$$

$$I_{LC} = \frac{f_d}{30C_s Z_{LC} \omega_d^3} \left( 30I_o t_{res}^2 \omega_d^3 + 60I_o f_d \sin(2\omega_d t_{res}) \right) + \frac{f_d}{30C_s Z_{LC} \omega_d^3} \left( 15I_o \omega_d \cos(2\omega_d t_{res}) + 108C_s t_{res} \omega_d^3 \right) - \frac{f_d}{30C_s Z_{LC} \omega_d^3} \left( 40I_o f_d t_{res}^3 \omega_d^3 - 60I_o f_d t_{res} \omega_d \cos(2\omega_d t_{res}) \right)$$

(2.13)

$$gain_{RCS} = bI_{LC} \tag{2.14}$$

$$V_s = \frac{I_{fault}}{gain_{RCS}} \tag{2.15}$$

where:

- $Z_{LC}$ : characteristic impedance ( $\Omega$ )

- $I_o$ : RCS current with  $V_s$ =1 V

- $I_{LC}$ : approximate RCS current gain per volt of  $V_s$  after  $t_{res}$  seconds (A/V)

- $f_d$ : resonant frequency of RLC circuit (Hz)

- $gain_{RCS}$ : gain of entire commutation branch (A/V)

- b: number of RCS modules in parallel

- $V_s$ : estimated voltage to pre-charge  $C_s$  (V)

- $I_{fault}$ : expected fault current magnitude (A)

The RCS is controlled with a square wave signal of 0.5 duty cycle to generate the ramping resonant current. Switches S2 and S3 can be turned on to create a positive sinusoidal pulse and vice versa for S1 and S4. The corresponding gate pulses and resulting current can be seen in Fig. 2.4. Because the current injected into the VI is the inverse of the resonant current, the maximum peak of resonant current must occur in the positive portion of the sinusoidal waveform to cancel the fault current.

Figure 2.4: Typical control signals to generate resonant current in the RCS

Table 2.2 shows the criteria and resulting phase delay of the waveforms for timing the peak pulse.

Using a simple square wave control scheme, as detailed, has benefits in simplicity and loss management. Since the gates of the MOSFETs are turned on and off at the instance each reversal is completed, then the MOSFETs are inherently zero-current switching. In other words, the switching losses are minimized since little to no current is flowing through the MOSFET during its switching event. All losses are therefore associated with conduction losses. This increases the capabilities of the RCS since the MOSFET's junction temperature will not rise quickly.

Note that PWM strategies could theoretically be implemented with the H-bridge converter [23]. This could regulate the RCS current to a specific magnitude. Current regulation may also be theoretically achieved by leveraging the LC transfer function gain at different frequencies. If the magnitude of the resonant current could be held

| Reversals | Starting Pair | S1, S4<br>Phase Delay (s) | S2, S3<br>Phase Delay (s) |

|-----------|---------------|---------------------------|---------------------------|

| Even      | S1, S4        | 0                         | $\pi/\omega_d$            |

| Odd       | S2, S3        | $\pi/\omega_d$            | 0                         |

Table 2.2: RCS Pulse Delay According to Reversals

at the magnitude of the fault current, then the zero-current-crossing would be longer lasting and allow the mechanical contacts more time to build dielectric withstand. This would further decrease the likelihood of the arc re-establishing or restriking. However, PWM or variable frequencies would intersperse switching events across each reversal. This would drastically increase switching losses due to the large currents. The main obstacle in using PWM would be the management of these switching losses. Therefore, the resonant frequency 0.5 duty cycle control scheme described earlier in this section is used for its zero-current switching characteristics.

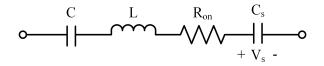

## 2.2 RLC Sizing

The equivalent series RLC circuit network for the RCS is given in Fig. 2.5. For an RLC circuit, there are three basic responses: underdamped, overdamped, and critically damped. All are classified according to how much damping or resistance present in the circuit. Underdamped circuits exhibit harmonic ringing, and overdamped or critically damped circuits slowly approach a steady state value with no ringing. The goal of this inverter is to create a continuously growing ringing current, so we must create an underdamped circuit for the RCS. In other words, we want to minimize the amount of resistance present in the series RLC network. In fact, it is counter-productive to have damping since it decreases the peak-to-peak current gain. Therefore, the resistance in our circuit is considered as the parasitic on-state resistance of the MOSFET switches,  $R_{on}$ . Since WBG devices are used, this is typically

Figure 2.5: Equivalent RLC circuit of the RCS

very small especially since multiple switches are used in parallel to increase their current capabilities. The source capacitance,  $C_s$ , is much greater than the capacitance of the resonant capacitor. Therefore, it does not have significant effect on the resonance of the circuit.

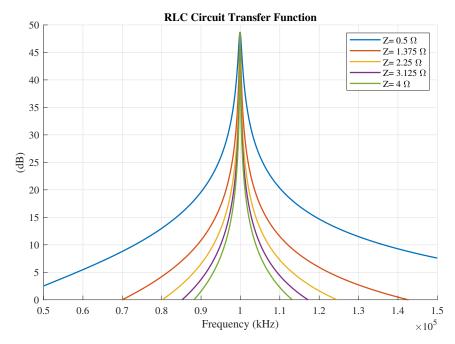

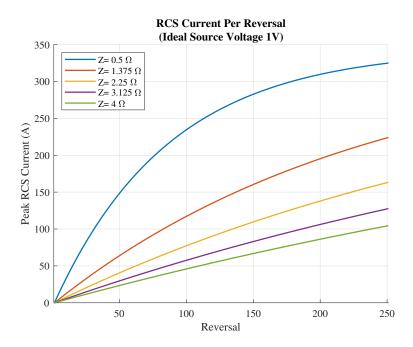

Fig. 2.6 shows the transfer function of the RLC network about the resonant frequency of 100 kHz for different impedances of L or C. The transfer function does not change at resonance, since the impedance of the RLC circuit is purely resistive, but increasing the impedance of the LC portion controls the current-over-voltage gain at all other frequencies. Presumably, as mentioned in Section 2.1.3, the gain at other frequencies could theoretically be utilized to regulate the RCS current. The main drawback to this approach is the substantial switching losses.

The peak magnitude at each reversal is shown in Fig. 2.7 for many reversals. These are compared with different combinations of LC impedance. Increasing the impedance controls the ramping rate of the RCS current. With greater impedance, the current

Figure 2.6: Transfer function of RLC network with different LC impedances

Figure 2.7: RCS reversal peak magnitude with different LC impedances

ramps less quickly but sustains longer linear growth. With lower impedances, a high ramping rate is possible, but the current saturates much more quickly. The high current differential may negatively affect electromagnetic interference and device lifetime. For future studies, the impedance of the RCS should be optimized against parameters such as device lifetime, peak device junction temperature, power density, and speed of interruption. For the purposes of this work, the impedance of 1.59  $\Omega$ is chosen as sufficient for its relatively quick ramping and sufficient linear growth before saturation. At 100 kHz, this impedance results in an equivalent inductance of 2.53  $\mu$ H and a capacitance of 1.00  $\mu$ F. Using the impedance, other inductances and capacitances can be easily calculated for any desired resonant frequency.

## 2.3 Conclusion

An improved hybrid DC circuit breaker is introduced in this chapter, which is based upon a solid state RCS to achieve ultra-fast induction of current-zero crossings. The RCS leverages the fast-switching WBG MOSFETs to achieve high frequencies of resonance. The control strategy of the RCS module is introduced to induce the current zero and quench the arc. The mechanical switch, a VI, is utilized as the sole component in the conduction branch to achieve high efficiency. To improve interruption speed, the VI is equipped with an actuator that combines permanent magnets and Thomson coils. For overvoltage mitigation during the fault interruption, a MOV is used for aircraft applications of 2.4 kV, and a SA is used for 20 kV shipboard. Combining this technology, the proposed breaker concept can interrupt faults within 500  $\mu s$ . Modeling and simulation analysis will be presented in the following chapter to further investigate the performance of the improved hybrid DC circuit breaker.

Copyright<sup>©</sup> Trevor M. Arvin, 2022.

# Chapter 3 Modeling and Simulation of Resonant Current Source Based Hybrid DC Breaker

#### 3.1 WBG MOSFET Modeling and Considerations

The thermal performance of the WBG MOSFETs are closely related to the maximum fault current capabilities of the RCS. Using information provided on the MOSFETs' datasheet, a thermal model can be developed such that the junction temperature of the devices can be monitored during fault interruption. This model, built in PLECS simulation software, takes into consideration the conduction losses, switching losses, and transient thermal impedance.

Since the source voltage of the WBG devices is decoupled from the DC bus, low voltage semiconductor devices can be utilized. This significantly reduces the number of devices and implementation cost. The main consideration for sizing the MOSFETs is having a sufficiently high current carrying capability. As a rule of thumb, the continuous DC current rating can be used to quickly compare different MOSFETs. For the 2.4 kV aircraft application, the EPC2022 GaN MOSFET (100 V, 90A continuous,  $150^{\circ}C$ ) [24] is used. Three parallel combinations of two in-series devices are used per leg of the H-bridge to give a maximum source voltage of 200 V. For the 20 kV shipboard application, the Cree CAS325M12HM2 SiC MOSFET half-bridge module (1.2 kV, 256 A continuous,  $175^{\circ}C$ ) is simulated [25]. In a physical application, this choice has the added benefit of decreased parasitic inductance between MOSFET connections due to its modularity, and the half-bridge structure lends convenience to building the H-bridge. Two half-bridge modules in parallel are used on each side of the H-bridge to increase the peak resonant current capabilities.

The lifetime and efficiency of the circuit breaker is dominated by its normal operation mode, so the MOSFETs lay dormant for most of the breaker's life. This mode is what determines the efficiency of the breaker since the losses during the fault interruption are small in proportion to breaker lifetime. Therefore, the losses during fault interruption are neglected. Instead, the objective is to ensure that a fault can be safely and reliably interrupted. There must be minimal damage or thermal stress to the components of the breaker. For this reason, the maximum junction temperature of the WBG devices is kept below  $100^{\circ}C$ . The ambient temperature for the aircraft simulation is room temperature  $25^{\circ}C$ , and the worst case scenario is simulated for shipboard at  $50^{\circ}C$ .

Due to the nature of the resonant current, the MOSFETs switch at every current zero of the RCS. The losses of the devices are therefore dominated by conduction since the switching losses are minimized. There is a tradeoff between the number of reversals possible and the peak current. In general, larger numbers of reversals necessitates longer conduction times and higher junction temperatures. However, this also decreases the necessary source voltage as it allows more time for the RCS to build its current. This is beneficial when considering lifetime and its dependency on temperature swing. The higher the peak-to-peak current difference results in more drastic junction temperature swings and uneven junction temperature distribution among the semiconductor devices. This is detrimental to RCS lifetime and reliability. Therefore, a balance must be struck between reversal number and semiconductor device stress.

#### 3.2 Vacuum Interrupter Modeling

The focus of this study is on the power electronic breaker circuits and how the other components behave as circuit elements. For this reason, it is important to model the effects of the VI from the circuit's point of view. It can be modeled behaviorally using a black box arc model. Other models can be used, but they vary widely in complexity and scope. The functional processes of VI operation and arcing are described in this section.

In DC conditions above a few tens of milliamperes and a few volts, an arc will be established between two current-carrying contacts when they separate [26]. Despite the separation, the arc will allow the current to continue flowing across from contact to contact. It is crucial that the arcing time be kept to a minimum. The longer an arc is allowed to form the more severe the damage on the contact's metal surfaces will be [27]. This negatively affects the lifetime of the vacuum interrupter.

When the mechanical contacts first separate, a molten bridge of contact material will connect the two surfaces. As the contacts continue to displace, the molten bridge will rupture and disperse metal vapor about the insulation medium (e.g., air, SF6, vacuum, oil). This metal vapor provides the conditions for the arc to initiate, especially in vacuum mediums. Afterwards, the arc may stabilize in the form of a diffuse or columnar arc. If the insulation medium is gas, then the arc will be composed of a low resistance plasma. Once the arc stabilizes, it will appear as a low resistance and low voltage drop to the circuit.

To quench this arc, a zero current crossing must be provided either naturally or artificially. Once this is achieved, the arc no longer has enough power to sustain itself and collapses. The behavior of the arc can be approximated using a variety of different black box arc models, which will be explained in the next section.

## 3.2.1 Black Box Arc Model

The behavior of an arc is physically complex and stochastic in nature. However, there are models that simplify their processes such that they can be replicated and modeled as an electrical component. Black box arc models (BBAM) are one such model that make it possible to analyze how arcing affects the circuit (e.g., arc resistance, voltage transients, failures to quench, etc.). This type of modeling is commonly used in AC circuit analysis, but in other works it has been been applied in DC with desireable results [28–32]. Other arc models have also been proposed recently that are derived specifically for DC conditions [33].

There are many variants of the BBAM that can be used with varying fidelity, parameters, and complexity. In general, the BBAM models the arc as voltage dependent conductance. This can be conveniently manipulated using Ohm's law to make a voltage dependent current source. The two most popular models are the Mayr and Cassie. These are widely used, and many other models are based upon them. Mayr and Cassie models are based upon the energy conservation principle and use a series of convenient assumptions to derive their models [34]. The equation for the Cassie model is provided in Equation 3.1, and the Mayr is given in Equation 3.2.

$$\frac{1}{g}\frac{dg}{dt} = \frac{1}{\tau} \left(\frac{u_{arc}^2}{u_0^2} - 1\right) \tag{3.1}$$

$$\frac{1}{g}\frac{dg}{dt} = \frac{1}{\tau} \left(\frac{gu_{arc}^2}{P_{out}} - 1\right)$$

(3.2)

where:

- g: arc conductance (S)

- $\tau$ : arc time constant (s)

- $u_{arc}$ : instantaneous arc voltage (V)

- $u_0$ : arc reference voltage (V)

- $P_{out}$ : cooling power of arc (W)

The two models can be considered complementary to each other. In other words, the models are suited for different arcing conditions due to their various assumptions. Other derivative models of the Mayr and Cassie exploit this relationship by combining the two to increase accuracy. The Mayr is most suited to high voltage arcs in the low current regime (<500 A and near current-zero). However, the Cassie model well suits high voltage arcs in the high current regime (>500 A and away from current-zero). By combining both, the resulting model can better represent arcs in both regimes. The Mayr and Cassie models are heavy simplifications of arcing behavior, so they tend not replicate experimental data well numerically. Instead, they are good qualitative models that describe arcs behaviorally and their effect on the circuit [35].

The motivation of other models that are derivative of Mayr and Cassie is to increase the quantitative accuracy. One such model that is commonly employed is the Schwarz model. In simplest terms, it can be thought of as a combination of both Mayr and Cassie. Both models can be found by manipulating certain parameters of the Schwarz model. The equation of the Swcharz model is given in Equation 3.3 [36].

$$\frac{1}{g}\frac{dg}{dt} = \frac{1}{\tau_0 g^{\alpha_s}} \left(\frac{g u_{arc}^2}{P_0 g^\beta} - 1\right)$$

(3.3)

where:

-  $P_0$ : constant factor of cooling power (W)

- $\tau_0$ : constant factor of arc time constant (s)

- $\alpha_s$ : exponential term of time constant

- $\beta$ : exponential term of cooling power

The Schwarz model is flexible enough to perform well in both high and low current regimes. This increases its usefulness in studying arc establishment, stability, and quenching [37].

The assumptions involved in deriving this model are as follows:

- Arc temperature varies exponentially with time

- Arc cross-sectional area is constant

- Power loss in the arc column is constant

- Arc time constant and cooling power are exponential functions of conductance

The assumption that the arc time constant and cooling power are exponential is what enables this model to easily match experimental data. There is no physical justification for this relationship, but it is mathematically convenient and performs well in practice. For the upcoming simulation, the Schwarz BBAM is utilized for its relative simplicity and its ability to accurately model arcing behavior.

By varying the parameters of the model, the arcing behavior can be changed.  $\tau_0$ and  $\alpha_s$  control the initiation time and delay of the establishing arc.  $P_0$  and  $\beta$  are similar to  $u_0$  in the Cassie model since they control the peak value of the overvoltage. By increasing this variables, the arc is easier to quench.  $\tau_0$  is also analogous to the insulation level of the mechanical contacts themselves while  $P_0$  is to the maximum breaking capacity of the contacts [31, 32]. By varying these parameters, the model can be fitted to experimental arc data, or an arbitrary model can be established.

| Category   | 2.4 kV Aircraft | 20 kV Shipboard |

|------------|-----------------|-----------------|

| $	au_0$    | 30  ns          | 20 ns           |

| $\alpha_s$ | 0.20            | 0.20            |

| $P_0$      | 50  kW          | 260 kW          |

| β          | 0.30            | 0.50            |

Table 3.1: Simulation Parameters of Schwarz Arc Model

In the upcoming simulation, a parameter sweep is utilized to tune the model for an arbitrary VI. The criteria is such that a stable arc is established upon contact separation and is quenched following a current zero crossing. The parameters of the Schwarz BBAM for each application are provided in Table 3.1

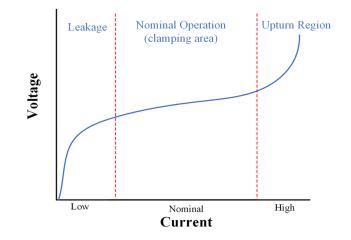

## 3.3 Overvoltage Mitigation Modeling

MOVs and SAs are nonlinear devices used to divert surges and clamp overvoltages. They are commonly placed in parallel with circuit breakers for clamping purposes. The RCS-HDCB is aimed at 2.4 kV aircraft and 20 kV shipboard distribution systems. A MOV can be used for the relatively lower voltage of aircraft, but an SA is a better fit for shipboard to account for the greater voltage and energy demands. A surge arrester is simply a stack of MOVs such that they can handle greater ratings. This section details the models used for the simulation of both the 2.4 kV and 20 kV MVDC systems.